# [Final] Past Exams - 2020 and Older #1041

Jero Wang STAFF 12 months ago in Exam – Final

You can find the past exams here: https://cs61c.org/fa23/resources/exams/. Please check the linked past Piazza/Ed Q&A PDFs first before asking here. Many of the questions are already answered in those! Video walkthroughs (if available), are also linked on that page!

When posting questions, please reference the semester, exam, and question in this format so it's easier for students and staff to search for similar questions:

#### Semester-Exam-Question Number

#### For example: SP22-Final-Q1, or SU22-MT-Q3

Elana Ho 12mth #1041adf 🤇 🗸 Resolved

b) Mark the following questions as either **True** or **False**:

| True  | <b>⊖False</b> | If we have a TLB which contains a number of entries equal to MEMORY_SIZE / PAGE_SIZE, every TLB miss will also be a page fault.          |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------|

| ⊖True | False         | If we change our TLB to direct-mapped, we're likely to see fewer TLB misses.                                                             |

| ⊖True | False         | Every TLB miss is equally expensive in terms of the amount of time it takes for us to resolve our virtual address to a physical address. |

| OTrue | False         | A virtual address will always resolve to the same physical address.                                                                      |

**\_\_\_\_\_** If we have a TLB which contains a number of entries equal to MEMORY\_SIZE / PAGE\_SIZE, every TLB miss will also be a page fault.

for fall 2018 final QF1b, why is the first one true?  $\odot~\cdots$

## - Andy Chen STAFF 12mth #1041aea

I think MEMORY\_SIZE is meant to be the size of virtual memory, so MEMORY\_SIZE / PAGE\_SIZE would be equal to the number of virtual pages. The page table contains a mapping/entry for every virtual page. This means that the TLB can hold all of the information in the page table, so there will never be any information that is not in the TLB (TLB miss) but in the page table.

$\bigcirc$  ...

Anonymous Viper 12mth #1041adc (Unresolved

#### SU20-Final-Q6ciii)

Why is the state from proc 0's point of view owner and not shared. I narrowed it down to either shared or owner and my thought process was that since shared says we haven't modified this block which we haven't and that we are not allowed to make modifications which process 0 can't since it only handles even indices it should be shared. Owner on the other hand necessitates that it is the only thread allowed to modify it, how can that be the case for proc 0 which only handles even indices?

799 VIEWS  $\bigcirc$  ...

Anonymous Viper 12mth #1041aee Any chance anyone knows why this is the case?

```

Anonymous Viper 12mth #1041adb Unresolved

```

SU20-Final-Q4b)

My thought process was that the minimum clock period is longest CL + tclktoq + setup time

the setup time + tclktoq is 4+3 = 7

For the longest CL I thought it would be reg 1 going down through or gate then through and gate then wrapping around above through the other and gate thus giving a value of 14 + 9 + 9 = 32 and thus my answer was 32 + 7 = 39. Why is it that the answer is 42 and not 39?

### Andy Chen STAFF 12mth #1041aeb

This one is a bit tricky, you are right about the longest CL path being through the OR and AND gate but the critical path in this circuit is actually from x\_input through the AND gate to the input of Reg1. For this path, from the rising edge of the clock, x\_input changes value after 30 ns (you can think of this kind of like a clk-to-q for x\_input), then it goes through the AND gate (9 ns), and then we add on the setup time (3 ns) which is 42 ns total. So in this case it's because x\_input sort of has a longer "clk-to-q" type delay than the other registers.  $\bigcirc$  ...

Anonymous Viper 12mth #1041aec

Ah so x\_input is a register in that case? I'm assuming since it says it switches value, it is essentially a flip flop so a register. That makes sense, thank you!  $\bigcirc$  ...

Anonymous Oryx 12mth #1041ace Unresolved

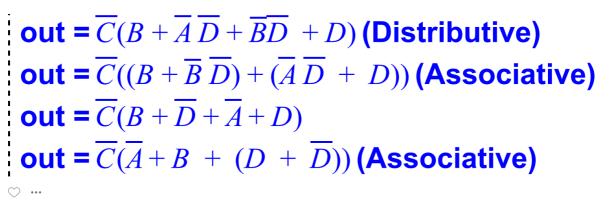

FA19-Final-Q5 d

how do we go from line 2 to line 3. this says

$$A + (\bar{A})B = A + B$$

but i couldnt find this anywhere

Anonymous Emu 12mth #1041acf One of the laws of Boolean algebra is X + YZ = (X+Y)(X+Z), which explains how A + !AB = A+B Line 2 becomes !C[(B+!B)(B+!D)+(D+!A)(D+!D)] which simplified, becomes line 3  $\bigcirc$  ... Anonymous Oryx 12mth #1041ada thanks!  $\bigcirc$  ... Anonymous Chicken 12mth #1041acd Unresolved su20-final-q12

can someone please walk me through the thought process of part a and what it is asking for? I don't get it.

♡ …

#### Fa19 Q9 c

Why is Translation and Data Access AMAT calculated separately? How do we know which is translation and which is Data Access. I ask this since we are accessing data throughout this process. First from TLB, then physical memory, then disk as well as L1 Cache. So why is the access from cache calculated separately?

#### <u>Q9) We've got VM! Where?</u> (15 pts = 2 + 3 + 5 + 5\*1)

Your system has a 32 TiB virtual address space with a single level page table. Each page is 256 KiB. On average, the probability of a TLB miss is 0.2 and the probability of a page fault is 0.002. The time to access the TLB is 5 cycles and the time to transfer a page to/from disk is 1,000,000 cycles. The physical address space is 4 GiB and it takes 500 cycles to access it. The system has an L1 physically indexed and tagged cache which takes 5 cycles to access and a hit rate of 50%. On a TLB miss, the MMU checks physical memory next.

| a) How many bits is the Virtual Page<br>Number?<br><b>27 bits</b>                                                                                                                                                   | <b>SHOW YOUR WORK</b><br>Number of reachable virtual addresses: log2(32 TiB) = 45<br>Bits needed to reach all addresses in a page: log2(256 KiB) =<br>18<br>So the virtual page number bits are: 45 - 18 = 27                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>b) What is the total size of the page table (in bits), assuming we have no permission bits or any other metadata in a page table entry, just the translation?</li> <li>14 x 2<sup>27</sup> bits</li> </ul> | <b>SHOW YOUR WORK</b><br>We need to figure out the number of bits in the physical page<br>number. It is the same method except we use the physical<br>address space:<br>Number of reachable physical addresses: $log2(4 \text{ GiB}) = 32$<br>So PPN size is $32 - 18 = 14$ . We do not have any metadata<br>bits so the total number of bits in a PTE is 14. To figure out<br>how many entries we need, we need to look at the total<br>number of virtual page numbers we have = 27. This means<br>we need $2^{27}$ entries in the page table. This means we need a<br>total of $14 \times 2^{27}$ bits in our page table. |

| c) What is the average memory access time<br>(in cycles) for a single memory access<br>for the current process? Assume the<br>page table is resident in DRAM.                                                       | SHOW YOUR WORK<br>Translation AMAT = 5 + %(500 + 2/1000(1M))<br>= 5 + %(500 + 2000)<br>= 5 + %(2500)<br>= 5 + 500<br>= 505                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 760 cycles                                                                                                                                                                                                          | plus<br>Data access AMAT = 5 + 50% (500)<br>= 5 + 250<br>= 255<br>AMAT (overall) = 505 + 255 = 760                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ) ***                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| nonymous Clam 12mth #1041acb Unresol                                                                                                                                                                                | ved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

1. How do we know this is a page fault. It could have been a page hit right? If we had access to the page table, we'd be able to verfiy so how do we know for sure that this is a page fault in this case?

2. Also, looking at the explanation, how do we know it's a new page?

#### 4. Virtual Reality! I Mean Memory...

Consider a system with 2 MiB of physical memory and 4 GiB of virtual memory. Page size is 4 KiB. Recall that the single level page table is stored in physical memory and consists of PTE's, or page table entries.

(a) (3.0 pt) If we choose to store seven information bits in each PTE, how big is the page table in bytes?

2<sup>21</sup> VPN contains  $log(\frac{2^{32}}{2^{12}}) = 20$  bits PPN contains  $log(\frac{2^{21}}{2^{12}}) = 9$  bits 9 bit PPN + 7 info bits = 16 bits per PTE 2<sup>4</sup> bit PTE \* 2<sup>20</sup> PTE's = 2<sup>24</sup> bit page table, or 2<sup>21</sup> bytes

(b) (3.0 pt) The page table starts off empty, then we make the following accesses: 0x00111999, 0x00234567, 0x005555FFF. If the page table begins at address 0x20000000, at what address can we find the PTE for the first access? (Your answer should be in hex)

```

0x20000222. 0x00111999 has a VPN of 0x00111. Each PTE is 2 bytes, so 0x00111 * 2 = 0x00222. 0x2000000 + 0x00222 = 0x20000222.

```

- (c) (2.0 pt) We have a fully associative TLB that also started empty but now contains the three entries from the accesses above. If we access 0x00556000 now, will we get a TLB hit, page hit, or page fault?

- TLB Hit

- $\bigcirc$  Page Hit

- $\bigcirc$  None of the other answers

- 🔵 Page Fault

- Page Fault. 0x00556000 is a new page

$\bigcirc$  ...

Anonymous Viper 12mth #1041aca (Unresolved

#### Su20-Final-Q1b)i)

I understand that to find the number of PTEs in L1, we need to multiply the number of L1 PTs by the number of PTE in an L1 PT. However why do we not do similar for L2 and instead multiply the number of L2 PTs by the size of the L2 PT? I also just don't get where 2^6 and 2^12 are coming from, where were these sizes defined and if it was from part a), how does it relate(ie can someone walk through their thought process for this part?)

Anonymous Wombat 12mth #1041aae **Resolved** Fa17-Final-Q10

I think this code can cause data race. Why it is correct?

```

double omp5(double arr[], int size) {

int n = 4;

int res[4] = \{0, 0, 0, 0\};

// num threads(4) runs the code block with 4

threads.

#pragma omp parallel num threads(4) {

int thread_id = omp_get_thread_num();

for (int i = thread_id; i < size; i+=n) {</pre>

if (arr[i] != 0)

res[thread_id]++;

}

}

return res[0] + res[1] + res[2] + res[3];

}

····

Justin Yokota STAFF 12mth #1041abe

Each thread accesses a different index of the array, so no data race is possible. It will,

however, cause a lot of thrashing and cache misses, so this code is likely slow.

\bigcirc ...

Anonymous Emu 12mth #1041aad (Unresolved

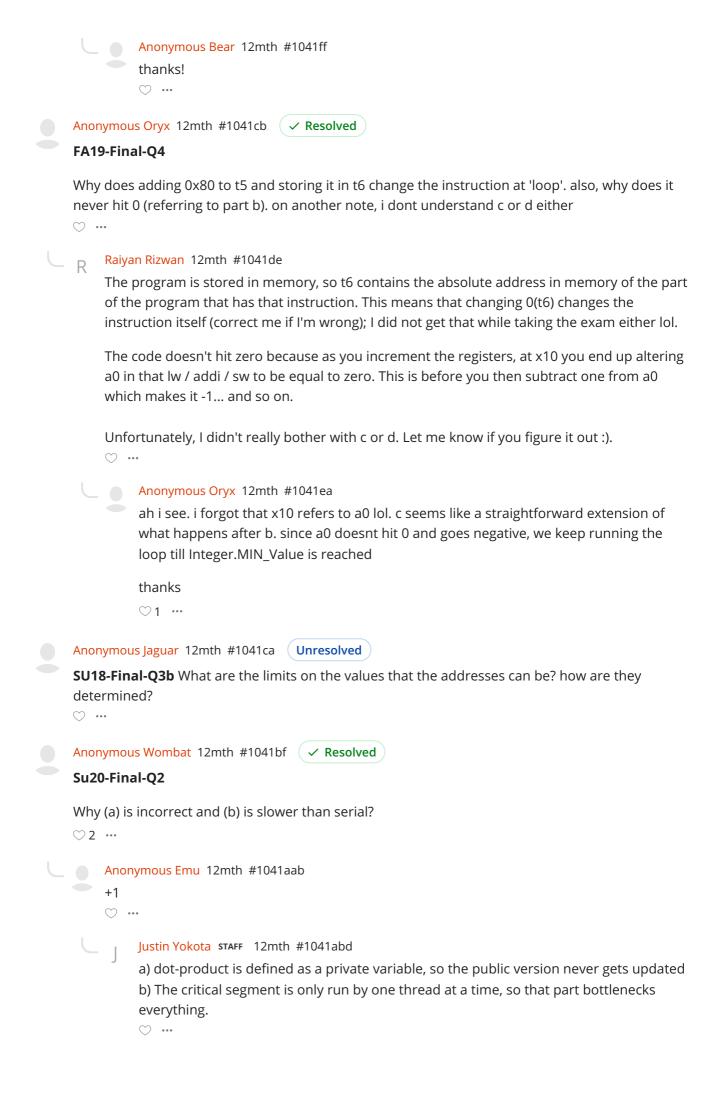

SU20-Final-Q6d-e-f

The prompt of the question says: Consider a computer which has 2 processors, each with their

```

own cache. Both have the same design: A 128 B cache size, 2-way set associative, 4 ints per block, write-back, and write-allocate with LRU replacement. Each cache takes in 20-bit addresses. Assume that ints are 4 bytes, and we are using the MOESI cache-coherence protocol.

(c) We decide to parallelize a for loop across these 2 processors, but instead of using OpenMP, we have each thread do a strided memory access, where processor 0 handles even indices, while processor 1 handles odd indices. However, the memory accesses are perfectly interleaved, i.e. the order of array accesses are still A[0], A[1], A[2], A[3]...

```

# define ARR_LEN 32

// A is located at address OxA0000

int A[ARR_LEN];

// Processor 0's loop

for (int i = 0; i < ARR_LEN; i += 2) {

A[i] += i

}

// Processor 1's loop

for (int j = 1; j < ARR_LEN; j += 2) {

A[j] += j

}</pre>

```

How do we reach a 1/2 hit rate. I don't really understand how MOESI caches work because we didn't really go over them in depth here, but I'm assuming that if the hit rate is 1/2, that means that on each iteration of the loop, the first access to A (read) is always miss (compulsory first iteration, coherency after that), the second access (write) is always a hit. If we have coherency misses, how would it be possible to have 0 times writing to main memory? That doesn't make sense at all. If you evict a block, you go to memory and write to update its contents with the contents of the block you just evicted? Can someone explain?

Also, how do we get a 3/4 of misses are coherency misses for part e. The question prompt says that each process has its own cache. When we load (i = 0) that's compulsory miss because that address has never been in cache 0. When we load (i = 1) that's compulsory miss as well because that address has never been in cache 1. Now, when we load i = 2 and i = 3, those are coherences, I could understand that. But wouldn't this mean that the true fraction and answer for question e would be 1/2 as well? I'm extremely confused

(d) (2.0 pt) What is the overall hit rate? Leave your answer as a fully simplified fraction.

1/2

The pattern above continues and repeats for all 8 blocks, giving us a 50% HR.

(e) (2.0 pt) What fraction of misses are coherency misses? Leave your answer as a fully simplified fraction.

3/4

0

Out of the 4 misses in each "access pattern block", 1 is compulsory, while the other 3 are coherency misses, so 75% of the overall misses.

(f) (1.0 pt) In total, how many times did we need to go to main memory to write-back?

As the array fits perfectly into the cache, we never need to evict an block and write-back, so 0.

♡1 …

Anonymous Emu 12mth #1041aac Unresolved SU20-FINAL-7d

I'm genuinely confused about every subpart in question 7 but part d doesn't really make sense to me. How did we get these answers?

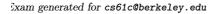

(d) (2.0 pt) After assembling jie.s to jie.o we have the following symbol table for jie.o. In linking max.o and jie.o we get dan.out. Which of the following could be true about 'sean' and 'jenny' after linking? Select all that apply.

34

Part (b)(ii)

The original question asks how many valid numbers can be represented with a 4 digit base 4 number using this scheme. Would 127 be a valid answer? There are 2 \* 4 \* 4 \* 4 representations total, but 0 is counted twice in the form 1000 and 0000.

(ii) Suppose rather than using a bias notation, we decide to do the following.

For each base 4 number, we will reserve the most significant digit to strictly be used as a sign bit. A digit value of 1 will indicate a negative number, and a digit value of 0 will indicate a positive number. Any other values will result in an invalid number. For instance:

$0003_4 = +3$   $1003_4 = -3$   $2003_4 = Invalid$

How many valid numbers can we represent with a 4 digit base 4 number using this scheme?

(ii) Suppose rather than using a bias notation, we decide to do the following.

For each base 4 number, we will reserve the most significant digit to strictly be used as a sign bit. A digit value of 1 will indicate a negative number, and a digit value of 0 will indicate a positive number. Any other values will result in an invalid number. For instance:

```

0003_4 = +3 1003_4 = -3 2003_4 = Invalid

```

How many valid representation can we represent with a 4 digit base 4 number using this scheme?

**Solution:**  $2^{*}4^{*}4^{*}4 = 128$

$\bigcirc$  ...

#### Justin Yokota STAFF 12mth #1041abf

This is ambiguous, I would say; some schools of thought treat +0 and -0 as different (for example, in doubles, 1/inf = +0, while 1/-inf = -0). This would warrant a clarification or valid ambiguity.

♡ …

Anonymous Clam 12mth #1041fd (Unresolved)

Fa19-Final-Q8

For the fourth step of part B, I'm failing to understand how a cache write can be a miss?  $\odot \ \cdots$

#### SP18-MT2-Q4a

hi, i am having trouble understanding the solution to Q4a. I thought that since this pipeline does not use double pumping or forwarding, the ID stage can only be done after the WB stage (eg: beq s1 s2 exit, shouldn't the D stage be stalled until c6 as well as xor s1 s1 s2). Additionally, why is E stage for the beg instruction stalled until c8 instead of starting at c7? Same question for lw instruction.

| Instructions   | Cycles |    |    |    |    |    |    |    |    |     |     |     |     |     |     |     |

|----------------|--------|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

|                | c1     | c2 | с3 | c4 | с5 | c6 | с7 | c8 | с9 | c10 | c11 | c12 | c13 | c14 | c15 | c16 |

| ori s1 x0 0xf  | F      | D  | Е  | М  | W  |    |    |    |    |     |     |     |     |     |     |     |

| andi s2 x0 0   |        | F  | D  | Е  | М  | W  |    |    |    |     |     |     |     |     |     |     |

| beq s1 s2 exit |        |    | F  | D  | *  | *  | *  | Е  | М  | W   |     |     |     |     |     |     |

| lw s1 0xc(s0)  |        |    |    | F  | *  | *  | *  | D  | Е  | м   | W   |     |     |     |     |     |

| xor s1 s1 s2   |        |    |    |    |    |    |    | F  | D  | *   | *   | *   | Е   | М   | W   |     |

| lw s1 0xc(s0)  |        |    |    |    |    |    |    |    | F  | *   | *   | *   | D   | Е   | м   | W   |

♡1 …

Anonymous Emu 12mth #1041fb Unresolved

#### SP20-Final -Q5b

I'm very confused about memory locations. I had the understanding that pointers were in the stack, and the values of pointers were allocated in the heap. For example, in the example below, I thought that u is in the stack and that v is in the heap. Now, we also know that v points to the address of u (v also in the stack).

Where my confusion starts is, if v points to the address of u, then \*v is just u, and we know that u is in the stack as specified above. So why does the exam solution say that u is in the heap.

Also, if u is in the stack, why would (u + 1) be in the heap. Wouldn't u + 1 also be in the stack? I'm just generally confused about what is considered to be in the stack and in the heap when it comes to pointers, as I had the understanding that pointers are in the stack, and what the pointers are pointing to are in the heap.

m generated for cs61c@berkeley.edu

#### (b) I Forget Where This Data Goes

For each question, select the option which best describes what an operation would evaluate tc operation would lead to something which is not a valid address, select "Not an Address". Consi snippet of a C program:

```

void foo() {

int64_t w = 4;

int64_t* u = malloc(100 * sizeof(w));

int64_t** v = &u;

}

```

#### Anonymous Heron 12mth #1041fa ( ✓ Resolved )

#### Fa19-Final-Q2d

The answer says 0x03 translates to ETX on the ascii table, but the ascii table provided on the reference sheet only starts at 0x20 Hex value and nothing before. Will we be expected to memorize/have written down the values before that?

|          | and<br>und<br>prin<br>prov<br>cha<br>fron | <pre>uint32_t *) variable c in little-endian format we call printf((char *) &amp;c)? If an error or lefined behavior occurs, write "Error". If nothing is ited, write "Blank". Please refer to the ASCII table vided on your reference sheet. For non-printable racters, please write the value in the Char column in the table. For example, for a single backspace racter, you would write "BS". ETX</pre> | Since the data is in little-endian format, the first<br>byte printed is 0x03, which corresponds to ETX.<br>The second character is 0x00, which is NULL,<br>the null terminator. printf doesn't read past the<br>first null terminator, so we finish printing after we |

|----------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                           |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                       |

| Catheri  | ne Var                                    | Keuren staff 12mth #1041abc                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                       |

| It looks | s like 1                                  | the FA19 final had a different refe                                                                                                                                                                                                                                                                                                                                                                          | erence card with 0x03 on it. You are not                                                                                                                                                                                                                              |

| expect   | ed to                                     | memorize any additional ASCII, a                                                                                                                                                                                                                                                                                                                                                                             | nd if we include anything related to ASCII                                                                                                                                                                                                                            |

|          |                                           | on the test, it will use the values i                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                       |

$\bigcirc$  ...

Anonymous Goose 12mth #1041ee 🗸 Resolved

#### Fa19-Final-Q8b

I don't understand why the fourth line in the solutions (ARRAY[i] write CONFLICT -> MISS) is a miss. In line 1 and 2, we put the block that contains ARRAY[i] into the cache, so I would assume when we access ARRAY[i] in the fourth line, is it a hit?

| <u>Q8) Th</u>                                              | is is for all                                                                                    | the money                                                                                                | <u>/! (</u> 15 p  | ts = 3 +         | 7 + 5)                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| direct-r<br>blocks.<br>integer<br>block-a<br><b>a)</b> Cal | napped L1 o<br>We have 4<br>is 4 bytes. <sup>-</sup><br>ligned.<br>culate the n<br>ex, and offse | a single-level,<br>cache with 16<br>GiB of memo<br>The array is<br>umber of tag<br>et <b>bits</b> in the | 5-byte<br>ory. An | int AR<br>int ma | e LEN 2048<br>RAY[LEN];<br>in() {<br>r (int i = 0; i < LEN - 256; i+=256) {<br>ARRAY[i] = ARRAY[i] + ARRAY[i+1] + ARRAY[i+256];<br>ARRAY[i] += 10;                                                                                                                                                           |

|                                                            | T:22                                                                                             | I:6                                                                                                      | 0:4               | ŀ                | SHOW YOUR WORK           Offset: log2(block size) = log2(16) = 4           Index: log2(cache size / block size) = log2(1 KiB / 16) = log2(64) = 6           Tag:           First find total address bits log2(4 GiB) = log2(4 * 2^30) = log2(2^32) = 32           Then 32 - Index - Offset = 32 - 6 - 4 = 22 |

| As                                                         |                                                                                                  | rate for the occesses expre                                                                              |                   | ove?             | SHOW YOUR WORK<br>Every iteration it's<br>ARRAY[i] read MISS<br>ARRAY[i+1] read HIT<br>ARRAY[i+256] read CONFLICT→ MISS<br>ARRAY[i] write CONFLICT→ MISS<br>ARRAY[i] read HIT<br>ARRAY[i] write HIT<br>3 MISSES, 3 HITS. 50% hit rate.                                                                       |

#### $\bigcirc$ ...

Catherine Van Keuren STAFF 12mth #1041abb

For this, an example might help. Imagine the address of ARRAY[I] is 0x00000400. Meaning our Offset = 0b0000, our index = 0b00000 and our tag = 0b0....01. This means that when we

put our entry into the cache we're putting it into index 0 with a tag of 1. When we jump to ARRAY[I+256], we're loading from address 0x400 + (256 \* 4 (times four to account for size of int)) (0x400). Thus when we add these together, we end up with a new address of 0x800. From this new address we get a Tag of 0b0...10 = 2 and an index of still 0 meaning that it would need to go in the same place as ARRAY[I] and thus is a conflict miss.  $\bigcirc$  ...

Unresolved

How do we get 27 for the number of bits in the PPN?  $\bigcirc$  ...

#### Fa18-Final-Q3

I am very confused on how to approach 3a. Where are we getting byte2+byte3 from and how does the table yield the answers in the chart? ···· ··

Anonymous Clam 12mth #1041dd Unresolved

### Su20\_MT1\_ 3b (ii and iii)

Can someone explain what we are storing when we store ra (which line address).

Also, why do we store ra?

What is the flow of this program i.e when does it reach input 5,6 and 7.

(b) Find the length of a null-terminated string in bytes. The function should accept a pointer to a null-terminated string and return an integer. Your solution must be recursive!

```

strlen:

__<CODE INPUT 1>__

beq t0, zero, basecase

__<CODE INPUT 2>__

__<CODE INPUT 3>__

jal strlen

__<CODE INPUT 4>__

jal strlen

__<CODE INPUT 6>__

__<CODE INPUT 6>__

ret

basecase:

__<CODE INPUT 8>__

ret

```

#### Fill in the following:

i. (0.75 pt) <CODE INPUT 1>

lb t0, 0(a0)

ii. (0.75 pt) <CODE INPUT 2>

addi sp, sp, -4

iii. (0.75 pt) <CODE INPUT 3>

sw ra, 0(sp)

iv. (0.75 pt) <CODE INPUT 4>

addi a0, a0, 1

v. (0.75 pt) <CODE INPUT 5>

addi a0, a0, 1

vi. (0.75 pt) <CODE INPUT 6>

lw ra, 0(sp)

vii. (0.75 pt) <CODE INPUT 7>

addi sp, sp, 4

```

\bigcirc ...

```

#### Fall-2019-Q9c

Why do we not need to consider page faults occuring for TLB hits? If page faults never occur for TLB hits, then why do we have a valid bit? Wouldn't valid bits be unnecessary if they just tell if the page is a resident of DRAM but page faults never occur since they're available in the TLB?

Thanks!

Raiyan Rizwan 12mth #1041ec

I believe it would not be considered a TLB hit if the valid bit is 0. Hence, the valid bit being off would be captured by the miss category (please correct me if I'm wrong).  $\odot$  …

Anonymous Grouse 12mth #1041da (Unresolved)

SP15-Final-F1C:

Why would separating the 2 loops allow the array\_size to be larger? Don't we still have the array a in memory even if it's done be written to? Also, do we not worry about page table taking up physical memory? It will be really helpful if someone can walk me through the thought process for this problem.

```

♡ …

```

Anonymous Wombat 12mth #1041ce (Unresolved)

#### Fa20-MT-Q5C

When applying forwarding to store instruction, which stage(EX or MEM) in the store instruction accepts the forwarded value?

For 2-3: Data, 2, Data, 2 in Version 1, why in case 2 the answer is Data, 2? I think forwarding can solve the data hazard?

```

♡ …

```

```

Anonymous Bear 12mth #1041cd Unresolved Su19-MT1-Q3:

```

```

1.

/* Function that takes in an array of integers, mallocs space for a new array,

* and copies the integers from the first array into the new array. It returns

* the new array.*/

int* copy_ints(int* arr) {

/* Allocates space to store all integers in arr. */

[ ] int* new = malloc(sizeof(arr)); // Can't use sizeof (arr), need to pass in a len

/* Iterates over all the elements in arr. */

[] for (int i = 0; i < sizeof(arr); i++) { // Can't use sizeof (arr), need a len

/* Loads an element from arr and stores it in new. */

[]

*(new + i) = *(arr + i);

}

/* Returns a pointer that can be dereferenced in other functions. */

[ ] return new;

}

[] no errors

```

What is the 'len' mentioned in this problem? I assumed that sizeof(arr) would calculate the total length in bytes, which would be sufficient for alloc'ing memory to store all integers  $\odot$  …

Anonymous Tarsier 12mth #1041cf IIRC sizeof doesn't work for pointer arrays on the heap.

Anonymous Rhinoceros 12mth #1041be (Unresolved

#### Sp19-Final-Q2d

Can I get an explanation on why the answer to this question is 2 pages? Is a "page table page" the same as a page table entry?

$\bigcirc$  ...

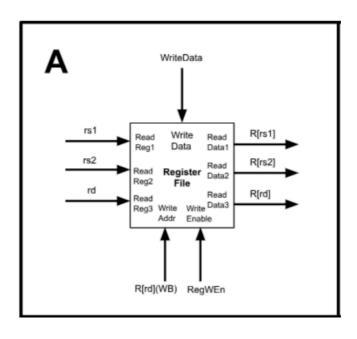

#### Sp19-Final-Q2a

What does Write Addr mean for this question. Also, what is R[rd](WB)? This is for the bottom left arrow/input.

♡ …

Sonika Vuyyuru STAFF 12mth #1041ef

"Write Addr" refers to write address, meaning the address that the data is being written to if you are writing to the Reg File. R[rd](WB) means the value in the rd register of the write-back stage. This syntax is explained in the problem description.

Anonymous Rhinoceros 12mth #1041bc Unresolved

**Sp19-Final-Q1c** (This question builds off the info in part (b))

For this question, my thought process is that after every 60 ms interval, we poll, which takes 1 ms of overhead. Therefore, the overall overhead= $1/(60+1) \times 100\% = 1/61 \times 100\%$ . However, the answer is 1/60. Why is that? Is overhead included in the polling interval of 60 ms?

(c) If there is *no* network traffic, what percentage of the CPU will be spent polling?

$Overhead = \_ \%$

Solution: 1.66% or (1/60) \* 100

#### SU18-Final-Q1.2

Suppose that the staff has implemented a function frame\_size which takes in a C function's name as a string and outputs how many **bytes** that the function's local variables would need in the function frame:

How was the answer obtained? I suppose the 8B comes from the 7 char of the array + the string terminator. Where do the other 8B come from though?  $\odot$  ...

Catherine Van Keuren STAFF 12mth #1041aba

I believe it comes from the two passed in arguments argc and argv.

♡1 …

Anonymous Grouse 12mth #1041af ( ✓ Resolved

Su18-Final-Q12

Suppose we have a 5-disk RAID 3 system. Compared to a 5-disk RAID 5 system that is **byte striped**, fill in all the bubbles for the data request patterns / characteristics where RAID 5 **strictly outperforms** RAID 3.

(A) long sequential reads

(D) small random reads

(B) long sequ

(E) small random

B long sequential writesE small random writes

$\bigcirc$  recovering from 1 disk failure  $\bigcirc$  capacity

2 \* 4B + 8B = 16 B

Are RAID 3 and small random read /write in scope? I don't remember they are covered in lecture.  $\odot~\cdots$

Catherine Van Keuren STAFF 12mth #1041aaf

Raid 3 is out of scope. You should typically know what small random read/writes are in comparison to long sequential read/writes when it comes to redundancy or cache replacement policies, but I would say that if the terminology isn't in lecture/discussion then it will most likely not be emphasized.

♡ …

#### SP18-Final-Q12-h

Does anyone have any good resources to look at for problems like these? I'm really lost on how they did this, given that we only have the virtual address  $\odot$  ...

instruction, similar to how it may have been done in discussion:

| C1 | C2 | C3 | C4  | C5  | C6  | C7 |

|----|----|----|-----|-----|-----|----|

| IF | ID | EX | MEM | WB  |     |    |

|    | IF | ID | EX  | MEM | WB  |    |

|    |    | IF | ID  | EX  | MEM | WB |

In order to figure out where stalls are needed (assuming absence of forwarding as specified by the problem), take a look at a pair of instructions where the first one sets the value of register rd, and the second register uses the value rd for some other computation. Then you have the case of either write-read or read-write

- write-read: similar to lecture, you are going to have to stall the first instruction such that the WB of instruction 1 and ID of instruction 2 are lined up.

- read-write: this is a little tricky, but you are going to want WB of instruction 1 to be 1 cycle before ID of instruction 2 since the WB input from instruction 1 will be output of the rd register 1 cycle later, aka when we have ID of instruction 2.

Hope this helps!

```

♡1 …

```

```

Anonymous Swallow 12mth #1041a

Resolved

```

```

SP18-Final-Q1(c)

```

(c) Given the following function in C:

```

int shifter(int x, int shift) {

if (x > 0) {

return x >> shift;

}

return -1 * (x >> shift);

}

```

Given y is a negative integer, and that shifter(y, 2) outputs 4, what is the range of values of y?

hint: -8 >> 1 = -4

Solution:  $-16 \sim -13$

Apparently, I have gaps in my understanding of how the bitwise shift works. Why y = -15, -14, and -13 would output 4? I get -1111 >> 2 = -0011 = -3  $\bigcirc$  ...

Anonymous Swallow 12mth #1041b Never mind. 2s complement is the answer.  $\bigcirc$  ...