# [Final] Past Exams - 2023 #1044

Jero Wang STAFF 12 months ago in Exam – Final

You can find the past exams here: https://cs61c.org/fa23/resources/exams/. Please check the linked past Piazza/Ed Q&A PDFs first before asking here. Many of the questions are already answered in those! Video walkthroughs (if available), are also linked on that page!

When posting questions, please reference the semester, exam, and question in this format so it's easier for students and staff to search for similar questions:

# Semester-Exam-Question Number

For example: SP22-Final-Q1, or SU22-MT-Q3

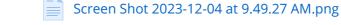

Anonymous Kookabura 12mth #1044babd

SP23-Final-Q4:

https://edstem.org/us/courses/43491/discussion/3970125?comment=9236636

I have the same question as the link above, but I still couldn't understand this - why is thrashing happening? I'm not sure why they have the same index (as for b we are indexing j and for a we are indexing i+j)

✓ Resolved

♡ …

Andrew Liu STAFF 12mth #1044babe

Remember that cache addresses use a T:I:O breakdown to find the index — if you check the bit addresses, you'll find that the index field of the blocks end up being the same.  $\bigcirc$  …

Anonymous Eagle 12mth #1044baba 🤇 🗸 Resolved

#### Sp23-Final-Q2

Why would the Branch comparator not be on the critical path? During the execute stage, don't we need to "wait" for the branch comparator to correctly set the Asel, Bsel signals?  $\odot$  …

N Nikhil Kandkur STAFF 12mth #1044babb #1044abfc 3,214 VIEWS

#### SP23-Final-Q7.12

Why do we need to include this line? I thought the calloc we did for codecopy initialized everything in codecopy to 0.

$\bigcirc$  ...

### Jero Wang STAFF 12mth #1044afde

This 0 is used to "erase" the branches and jumps, which are set when you  $\,{\rm memcpy}\,{\rm ed}\,\,\odot\,\,\cdots$

```

Anonymous Armadillo 12mth #1044afae ( ✓ Resolved

```

SP23-Final-Q8.3

How is the answer 200 minutes if the task list is (chip A: 1,3) (chip B:0) (chip C:2,4). I'm getting 210 minutes for my calculations

$\odot$  ...

Jero Wang STAFF 12mth #1044afdf

Could you show the math for 210? Here's what I'm getting:

Chip A does task 1 from t=0 to t=100, task 3 from t=100 to t=200 (task 0 is finished by t=50).

Chip B does task 0 from t=0 to t=50)

Chip C does task 2 from t=50 to t=110, task 4 from t=110 to t=170.  $\odot$  ...

# SP23-Final-Q8.3

For creating the task list, I don't remember how to come up with it. Are there any specific tips anyone has or any resources that review how to come up with the optimal task list?  $\odot$  ...

#### Jero Wang STAFF 12mth #1044afea

There's a homework question that's similar, but in general, I'd recommend just going with greedy as a starting point, then try to make some fine adjustments based on what you come up with!

$\bigcirc$  ...

Jiries Kaileh 12mth #1044aeed ( ✓ Resolved )

Just a general question, does the following equation hold for finding the local miss rate for a cache level?

LNC = Level n cache; LMR = local miss rate; GMR = global miss rate

LNC LMR = LNC GMR \* (1 / L(N-1)C LMR) \* (1 / L(N-2)C LMR) \* ... \* (1 / L(2)C LMR) \* (1 / L(1)C LMR)  $\odot$  ...

Andrew Liu STAFF 12mth #1044baca

This looks right to me; another way to think about it is that the LMR is just (# hits to cache level) / (# accesses to cache level), and you only access a cache if *all* previous cache levels have missed.  $\bigcirc$  ...

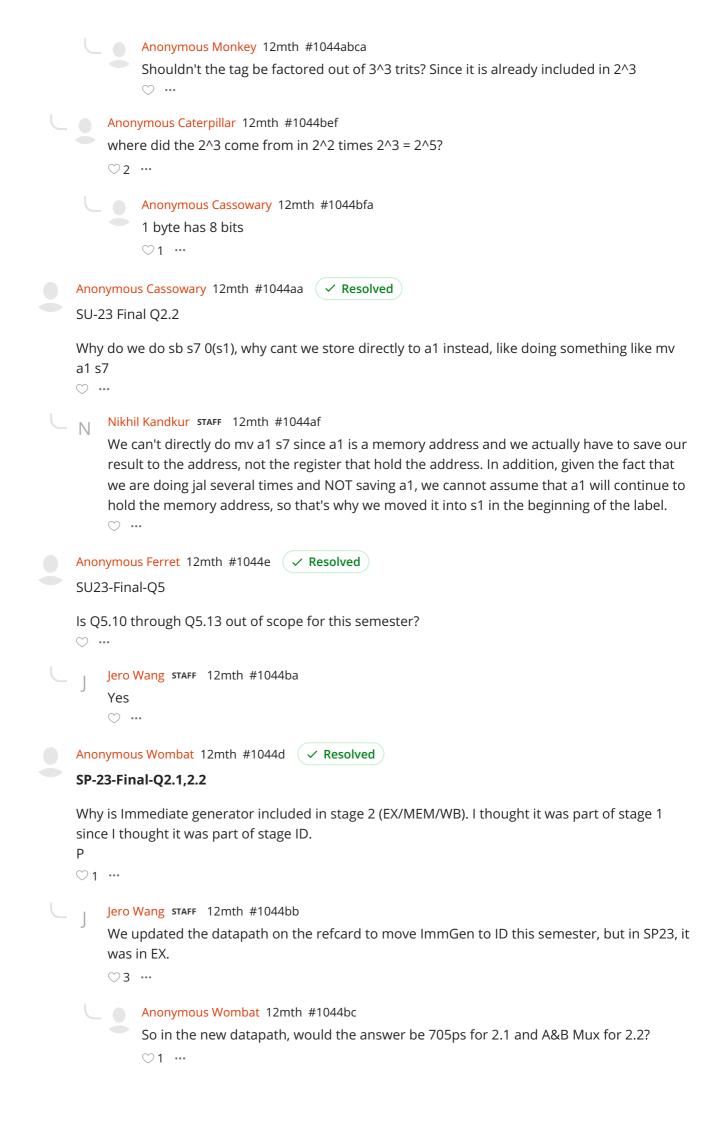

Anonymous Monkey 12mth #1044aeea ( ✓ Resolved

#### SP23-Final-Q2.1

Why do we only include stage 2 in the critical path for lw? In the discussion this was the full path:

lw = clk-to-Q + Mem-Read + max(RegFileRead + Mux(ASel), Imm-Gen + Mux(BSel)) + ALU + Mem-Read + Mux(WBSel) + RegFileSetup = 5ns + 300ns + 60ns + 100ns + 300ns + 15ns + 20ns = 800ns

How does switching around the stages decrease the critical path? Why do we not include RegFile Read over ImmGen if it is greater, and why do we only include the MemRead once? The solutions say that lw instructions only goes through stage 2, but it also needs to go through IF and ID. In this question, I am not sure how splitting the stages into 2 informs in that there will be two different critical paths from each one, when for 5 stages, we take the critical path of the whole circuit  $\heartsuit$  …

### Anonymous Monkey 12mth #1044aefa

Nvm, I didn't know that only the longest stage matters for a pipelined circuit. Is this information that was taught in lecture?  $\odot$  ...

Anonymous Capybara 12mth #1044aeff

could you explain why only the longest stage matters?  $\bigcirc$  …

Sonika Vuyyuru STAFF 12mth #1044afaa

Yes, this should be covered in lecture! It is also explained in question 3 of Discussion 8. I would suggest revisiting that for some more practice.

The main idea here is that when we pipeline the datapath, the longest stage constrains what we can set the clock time to be. The reason for this is that the same clock drives each of the stages, so even if another stage (like IF) takes less time, it needs to wait until the longest stage has completed it's execution to be able to move on to the next clock cycle.  $\bigcirc$  ...

Anonymous Spider 12mth #1044aedc ( ✓ Resolved )

SU23-Final-Q1.5 Why during a thread context switch, the entries of the TLB get invalidated? Do threads in a process share same memory space? If true, then why context switch here should invalidate TLB?

$\odot$  ...

Jero Wang STAFF 12mth #1044afdd

Yes, they do share the same memory space. In the real world, this is implementation specific - you can optimize it such that you don't need to flush if its the same memory space. It's just that this was how it was taught in the summer (verbatim from slides).

the answer says the shortest time is 9 hours, but I think it could take just 8 hours to finish the tasks. Is there anything wrong with my answer?

1 Ahj 3h 11 1h11 24 Bot my 8h 1/11 4h answer Gran 2 0 Bot. aven 9h. Evan answer

···· ··

Anonymous Ferret 12mth #1044aedd It takes EvanBot 3 hours to complete task 4.  $\bigcirc$  …

Anonymous Cheetah 12mth #1044aede

Thanks, I just realized that lol …

Anonymous Armadillo 12mth #1044aeab 🛛 🗸 Resolved

SP23-Final-Q1.1

Why does readArr ALU calculate rs1+rs2\*4. especially on the rs2\*4 part. I'm confused on the logic behind this.

♡ …

Anonymous Chamois 12mth #1044aeef

Integers are 4b wide, so we need to move it by 4 times.  $\bigcirc \ \cdots$

# Sonika Vuyyuru STAFF 12mth #1044aefe

Chamois has the right idea here. We want to read the byte at index rs2. 4 \* rs2 tells us how many bytes into the array we need to move to read the element at index rs2, since this is an array of integers and each integer is 4 bytes. We then add this to the pointer address given by rs1.

$\bigcirc$  ...

SU23-Final-Q3.13

I am confused why branch instruction don't have data hazards? if we add t0,t1,t2 then bge t0,t1,loop , this t0 depends on add instructions WB from previous.  $\bigcirc$  1 ...

Sonika Vuyyuru STAFF 12mth #1044aefd

This question asks what type of hazard can be *caused* by the long branch instruction. Since the branch instruction does not write back to an rd register value, it does not cause any data hazards in future lines. In the example you provided, we could say the add instruction causes a data hazard, which affects the next line, which happens to be a branch instruction. ♡1 … Anonymous Grasshopper 12mth #1044afad got it! ♡1 … Anonymous Grasshopper 12mth #1044adfa ( ✓ Resolved Su23-Final-Q2 is it okay for write 14 instead of 0b1110?  $\bigcirc$  ... Anonymous Cod 12mth #1044aeca I have the same questionn  $\bigcirc$  ... Sonika Vuyyuru staff 12mth #1044aefb ς Yes, that should be fine.  $\bigcirc$  ... Anshul Verma 12mth #1044addf ✓ Resolved Α sp23-final-q1.3 Q1.3 (3 points) Eddy noticed that the structure of writeArr is similar to an R-type instruction. However, when he tried to use the control signals for an R-type instruction, it didn't work. Which of the following control signals does he need to change to correctly implement writeArr? Select all that apply. PCSel RegWEn □ ASel MemRW □ BSel □ None of the above Solution: PCSel: always 0 for R-types, 0 for writeArr • ASel: always rs1 for R-types, also rs1 for writeArr because the ALU performs "rs1 + rs2 \* 4" • BSel: always rs2 for R-types, also rs2 for writeArr because the ALU performs "rs1 + rs2 \* 4"

• RegWEn: always 1 for R-types, but must be 0 for writeArr since it does not write to any register

MemRW: always 0 for R-types, but must be 1 for writeArr since it needs to write to DMEM

**Grading:** Each checkbox was graded as it's own true/false question, and selecting "None of the above" was treated as not selecting any of the other choices.

Hi, for this question why does RegWEn need to be changed? I figured that since writeArr does not write back anything to the registers that RegWEn would just not matter.

$\bigcirc$  ...

$\bigcirc$  ...

Robert Yang 12mth #1044adeb

I think the output of the writeback mux is always sent to the register file so if you don't disable RegWEn, rs3 will wrongly be changed.

Anonymous Magpie 12mth #1044adda ( 🗸 Resolved

What does "Since bits 11 and 0 are set" mean? And how does this correlate to the answer being N/A?

Q8.5 (1.5 points) 0xC61

Solution: N/A

Since bits 11 and 0 are set, it cannot fit into a floating point number with 8 mantissa bits, so it is not representable.

$\bigcirc$  ...

Andrew Liu STAFF 12mth #1044aead

That sentence means that bits 11 and 0 being set to 1. Remember that a floating point representation can only have as much precision as the bit width of its mantissa.

In this case, the precision needed is 11 bits, but the width of the mantissa is 8 bits, so this address is not représentable.

Anonymous Rhinoceros 12mth #1044adcf ( < Resolved )

SU23-Final-Q5

Regardless of your above answers, assume that we have 20-bit physical memory addresses, and 24-bit virtual memory addresses. Assuming that physical pages are assigned sequentially and the following 3 virtual addresses have been accessed, in order:

| Virtual Address | PPN |

|-----------------|-----|

| 0xABCDEF        | 0   |

| 0xAABBCC        | 1   |

| 0x202122        | 2   |

After accessing the previous three addresses, we access the following virtual addresses in order. For each access, fill out the corresponding physical address, and whether the access causes a page hit or a page fault. Assume that if a page fault occurs, then the next sequential physical page number is assigned to the virtual page number.

Q5.4 (1 point) 0xA01243

O Page Hit

Page Fault

**Solution:** The VPN is 0xA01 and the offset is 0x243. VPN 0xA01 has not been accessed before, so it is a page fault. Since it's a page fault, we use the next sequential PPN, which is 0x3, so the physical address is 0x03243.

Hi! For 5.4 to 5.9 we are only given this, how should we figure out the offset bit and VPN? I get how it usually work but in this case do we have enough info to figure out? I am so confused Thank you!

$\bigcirc$  ...

Andy Chen STAFF 12mth #1044aeac

Yeah I think there actually isn't enough information here, I think the question is assuming that we are using the same page size as earlier in the question (which was 4 KiB =  $2^{12}$  Bytes). I think the intent was to use that to figure out the offset, and then use the given physical address length and virtual address length to find out VPN/PPN.

♡2 …

Anonymous Quail 12mth #1044adaf ( ✓ Resolved )

## SP23-Final-Q1

The solution in 1.1 says: "The readArr instruction is similar to any other R-type instruction, except that the ALU operation performed must be rs1 + rs2 \* 4."

Am I right in thinking that it is different from the R type instructions not only because of the new ALU operation, but also because we would have to read from memory, so the WBSel would be different? I get that we don't have to add anything new to the data path for that part, but just wanted to make sure that my thought process is correct.

I just got a bit confused because to me the readARR instruction is more similar to some kind of load instruction, with the difference being that it uses a value stored in a register instead of an immediate, rather than to an R-type instruction

♡ …

# Robert Yang 12mth #1044aded

I completely agree with your last paragraph. I think the exam says readArr is similar to an R-type instruction just because R-type instructions take in 3 registers as input, and so does readArr. So load and R-types are both similar to readArr in different ways.

Anonymous Gerbil 12mth #1044acfc 🗸 Resolved

SP23-Final-Q2.3

How come Immediate is not an answer? Don't we need it in stage 2 as an input to the BSel Mux?

Nvm answered in #1044ea  $\odot$  …

Anonymous Cobra 12mth #1044aced 🗸 Resolved

SU23-Final-Q6

Could someone explain line 3 in the solutions? I get the "#pragma omp parallel for" part, but what does the "reduction (+: count)" do?

$\bigcirc$  ...

Anonymous Mandrill 12mth #1044aeaa

declares count as critical variable so no two threads modify at same time  $\, \odot \, \, \cdots \,$

Andrew Liu STAFF 12mth #1044aeae

The reduction introduces a privatized version of the variable that is collected via the + operator. Check out the OpenMP lab spec for some more details.

$\bigcirc$  ...

Anonymous Armadillo 12mth #1044acdd

Resolved

SP23-Final-Q5.3

Why is this a page fault? I thought the index in the page table shows that at address 0x3, the PPN is CBA8 so the answer would be CBA860  $_{\bigcirc}$   $\cdots$

Anonymous Cobra 12mth #1044acde

PTE 0x3561CBA8 is not valid, since 0x3 = 0b0011 (valid bit is 0). So we use the next free physical address in main memory.

♡ …

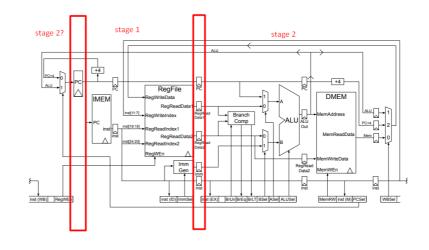

# SP-23-Final-Q2.1

Why do we include ImmGen in the 2nd stage? I think from the reference card ImmGen belongs to ID, which is included in the 1st stage in the question.

♡4 …

Anonymous Goldfinch 12mth #1044acef

SP-23-Final-Q2.1

I have same question here.

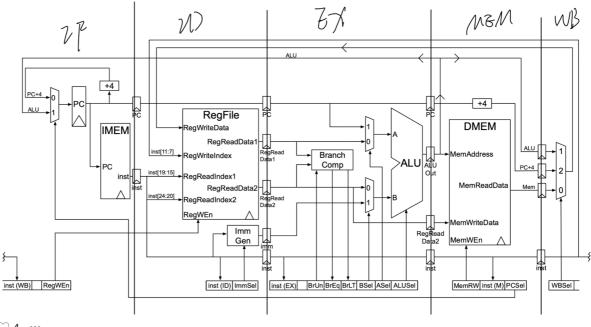

### Q2 IF Only ID Pipelined Better

In Project 3, we implemented a RISC-V CPU with two stages; stage 1 included IF and stage 2 included ID/EX/MEM/WB. For this question, imagine instead that we implement a two-stage pipeline with a different split; stage 1 will include IF/ID and stage 2 will include EX/MEM/WB (IF/ID/EX/MEM/WB are defined equivalently to the pipelined CPU on the reference card).

For Q2.1 and Q2.2, assume the following delays for each component. Any component not listed is assumed to have a negligible delay.

| Component           | Delay |  |

|---------------------|-------|--|

| $	au_{ m clk-to-q}$ | 35ps  |  |

| $	au_{ m setup}$    | 20ps  |  |

| Mux                 | 75ps  |  |

| Regfile Setup       | 20ps  |  |

| Regfile Read        | 175ps |  |

| Immediate Generator | 150ps |  |

| Branch Comparator   | 200ps |  |

| ALU                 | 200ps |  |

| Memory Read         | 300ps |  |

Question tells us that the datapath is split into two stages: stage 1 = IF/ID and stage 2 = EX/MEM/WB. So Imm generator shouldn't be included in the critical path right?

I'm also confused why DMEM is included. Isn't DMEM a type of register itself?  $\odot~\cdots$

Martin Lacsamana 12mth #1044acfe

If I'm not mistaken, they moved ImmGen into the ID stage this semester, so our answers would differ now. So yes, the ImmGen should be in stage 1.  $\bigcirc$  3 ...

N Nikhil Kandkur STAFF 12mth #1044aecf #1044bb © ···

Anonymous Magpie 12mth #1044acbd 🗸 Resolved

# SU23-Final-Q8.1

Through trial and error knowing that our exponent post-bias needs to be at least 6 (since  $2^6 = 64$ ), I figured out that we needed 4 exponent bits pre-bias. I just wanted to clarify if there was an easy intuition to see it being 4 bits or if we had to calculate the exp and bias equations to see which number of bits is at least 6.

♡2 …

Anonymous Chimpanzee 12mth #1044accf

I had the same question and approach  $\odot~\cdots$

Jero Wang STAFF 12mth #1044afbb

This was mostly trial and error for getting the exact number of exponent bits, since the bias depends on the number of exponent bits.  $\odot$  …

Anonymous Rail 12mth #1044acaf ( ✓ Resolved

#### SP23-Final-Q4.5

What is the formular we use for the different level of caches and is there any comprehensive

resource with all the formulas?  $\bigcirc$  …

Anonymous Kudu 12mth #1044accd last video of caches has a good example  $\bigcirc$  …

Anonymous Llama 12mth #1044abfc 🗸 Resolved

#### SP-23-Final-Q2.1

Why do we not include the Branch Comparator Delay into stage2 calculation? Could you please write out the equation to get the correct answer based on this sem's Datapath. I would also appreciate if you list the components for each stage.  $\odot$  ...

Robert Yang 12mth #1044acae 🛛 🞗 ENDORSED

I believe it's because the instruction that takes the longest is a load instruction, which doesn't use the branch comparator. You can also compute how long a branch instruction will take which of course does use the branch comparator, but this turns out to be less than the load instruction time.

♡ …

Anonymous Quail 12mth #1044adbf

If it's still relevant to you, my calculation ended up being: 35 + 75 + 200 + 300 + 75 + 20 = 705 $\bigcirc$  1 ....

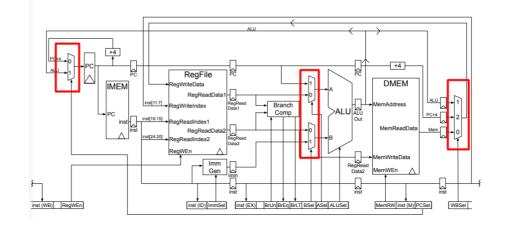

# SP23-Final-Q2.1

The calculation adds up 2 muxes but aren't there 3 muxes that we must go through in stage 2? See my screenshot below

$\bigcirc$  ...

Anonymous Rail 12mth #1044acaa

This mux that does in PC is part of stage 1 I believe (part of the IF stage)  $\odot~\cdots$

Robert Yang 12mth #1044acad

Hmm I thought everything has to be stored within a register between stages, so stage 1 begins after the first PC register which leaves the PC mux in stage 2. See the image below:

- ♡1 …

Anonymous Cobra 12mth #1044acec

Replying to Robert Yang

The MUX feeding into PC is part of stage 2, but if you look closely at the paths, its input is the ALU, not the WB MUX (which feeds into RegFile). Thus the longest path has two MUXes.

♡1 …

R Robert Yang 12mth #1044acee

A Replying to Anonymous Cobra

HOLY CRAP YOU'RE A GENIUS MAN/WOMAN THANK YOU SO MUCH this makes sense

2 ···

SP23-Final-Q5.4

Why is this a page fault? I thought that the page table was indexed by VPN and the VPN is 0x000003 which has a corresponding entry in the page table?

♡1 …

Anonymous Gnat 12mth #1044abfe Also confused on this same part ^  $\bigcirc$  ...

This comment was deleted

Anonymous Lion 12mth #1044acac

Wait to clarify I'm not confused about the TLB miss part but how it's a page fault. Page fault means that there's no entry for it in the page table but there is?  $\odot$  ...

Anonymous Kudu 12mth #1044accc 🔷 \land Replying to Anonymous Lion look at the valid bit (31/30) of the value in the page table - it's 0. ♡1 … Anonymous Cobra 12mth #1044aceb #1044acde ♡1 … Anonymous Kudu 12mth #1044abee ( ✓ Resolved SU23-Final-Q3.8/9 Aren't there 2 implicit zeroes since it can only jump by multiples of zero, as shown in the lecture slides as well? 2^11 and 2^19  $\bigcirc$  ... Jero Wang STAFF 12mth #1044afca Assuming you mean multiples of 4, no, you can jump in multiples of 2 (since RV32C instructions are 2 bytes), so there's one implicit 0.  $\bigcirc$  ... Anonymous Gerbil 12mth #1044abed ✓ Resolved SP23-Final-Q6.3 Is 0b110 a valid bit pattern for 0b0? ♡1 … Anonymous Cod 12mth #1044acbc **Q ENDORSED** I don't think so because the first parity bit and the data bit would sum to 1.  $\bigcirc$  ... Anonymous Kudu 12mth #1044acce no cause if it messes up a bit it can go into the region for 000, like 010 or 100, so it won't know if its 0 or 1  $\bigcirc$  ... Anonymous Zebra 12mth #1044abec ( ✓ Resolved SP23-Final-Q5.2 For this question, the solution says that the page table entry has the PPN in its last four bits. Is there a specific reason the PPN is in the last four bits? Is the location of the PPN specific to this question, or will the PPN always be in the final four bits of the page table entry?  $\bigcirc$  ... Anonymous Kudu 12mth #1044acda bits 0 to 16 have the ppn and typically the ppn always starts from the last n (16 in this case) bits of the PTE ♡1 … Anonymous Cod 12mth #1044abeb ( ✓ Resolved SP23-Final-Q4

Just to make sure I'm understanding this conceptually, but if say array a is of length 20, then would that result in a taking up two cache lines (one with index and one with index 1, but both with the same tag)? Because then we would also need to access address 0x1010 etc?  $\bigcirc$  1 ....

#### Anonymous Chamois 12mth #1044aeee

I think you need more than 2 blocks - seems to be 4? One block is 16b, so it can contain 4 integers (4b each). If we have 20, then we need 4 blocks. However, we know there can only be 4 blocks (64b / 16b), so that's the max.  $\bigcirc$  ...

•

#### Jero Wang STAFF 12mth #1044afec

20 elements or bytes? If its the former, then as Anon Chamois mentioned above, we need 5 blocks, which doesn't fit in our cache. If it's the latter, yes, it takes 2 cache lines.

If it's the latter, both would have the same tag, but different index.

♡1 …

Anonymous Llama 12mth #1044abdf ( ✓ Resolved )

### SP23-Final-Q5

Conceptual: When given a Virtual Address, what happens if:

1) when looking in TLB valid bit is 1 vs 0

2) when looking in TLB dirty bit is 1 vs 0

3) if TLB miss, page fault -> do you update TLB and PT, if so, how?

···· ··

Anonymous Kudu 12mth #1044acdb **R ENDORSED** assuming u are doing read operations:

1) 0 causes a page fault (I believe)

2) read operations wont care abt the dirty bit, write ones will evict it from DMEM to disk if dirty bit is 1

3) Yeah, you first update the PT and then copy that over to the TLB  $\odot$  1  $\cdots$

Anonymous Squid 12mth #1044abda ( ✓ Resolved

Q4.3 (2 points) For each block in their cache, SodaBot stores the tag and 2 additional bits of metadata (valid bit, dirty bit). What is the total number of bits used by the cache? Express your answer in terms of powers of 2 and 3.

```

Solution: 2 \cdot (3^3 + 2^5)

Each entry must contain 7 bits for the tag, 2 bits for the metadata, and 2^2 bytes (2^2 \cdot 2^3 = 2^5 bits) for the data. There are 2^1 entries total, for a total of 2 \cdot (3^3 + 2^5) bits.

```

Can someone explain where 3^3 and 2^5 came from? I understand there is 2 entries since there is only 1 bit for index. there are 7 tag bits +2 metadata bits so this is 9 bits also there are 2 offset bits.

N Nikhil Kandkur staff 12mth #1044aedb #1044cc

...

Anonymous Chimpanzee 12mth #1044abbb

Resolved

SU23-Final-Q8.1

Can someone explain why the answer is 4 bits? I thought we need 6 bits to represent 0-63

...

○ ··· Anonymous Manatee 12mth #1044abac (

Nikhil Kandkur STAFF 12mth #1044abdc

#### SU23-Final-Q8.5-8.7

#1044a

N

I don't quite get the explanation for 8.5 and or why we know that the lower 6 bits of the address is the chunk and the chunk address is the upper 6 bits. Can we get some help on that? Thank you!  $\odot$  …

✓ Resolved

Suvan Ravi 12mth #1044abad

The lower six is like the fraction of the chunk. Since anything less than multiples of 64 will be byte addresses inside the chunk. And the upper six bits become the whole number chunk addresses since they're multiples of 64.

$\bigcirc$  ...

Anonymous Jay 12mth #1044abaa ( 🗸 Resolved

#### SU23-Final-Q6

I'm somewhat confused on how this code correctly checks for palindromes based on the implementation in the solution. If we set left = 0 and right = width - 4, let's say we had a 10 integer array as such: [1,8,7,6,4,5,6,7,8,1], then left = 0 and right = 6, and the while loop would check 1,8,7,6 and the reverse of 6,7,8,1, confirm that they are palindromes, and set left = 4 and right = 2, thus failing the condition that left <= right, while maintaining that is\_palindrome is true. This inner while loop would then not check our middle 2 elements, which make the array not a palindrome, and would instead increment our count variable by 1. I'm not sure if there's something that I'm missing here? Could someone please explain the solution to the code?

♡1 …

#### Anonymous Lyrebird 12mth #1044aeaf **Rendorsed**

i had the same question. originally i made right point to the end of the right array instead of the beginning and then just subtracted 4 from that pointer value whenever vec2 was loaded. i am not sure if this has any bugs but i think this would account for all the values in the array.  $\odot$  …

Anonymous Emu 12mth #1044aafd ( ✓ Resolved

[SU 23 Q 8] For question 8.1 how do we get the standard bias of -7 or -3?

#### Q8 Non-quantum Computing

1 1

Suppose we have a chunk-addressable address space with 64 byte chunks. That is, address 1024 is 64 bytes away from address 1025 and 1 byte away from "address"  $1024 + \frac{1}{64}$ . To access every byte of this system, we can't use our standard integer binary addressing system, so let's use floating point!

Suppose that our memory "addresses" follow IEEE-754 floating point convention with 1 sign bit, and the number of exponent and mantissa bits that you will determine below.

Q8.1 (2 points) If we had 4KiB of memory, with chunk addresses 0, 1, 2, etc., what is the minimum number of exponent bits in our floating point memory address required to access every byte, assuming that we use a standard bias?

**Solution:** Given 4KiB memory and 64B chunks, we have 64 chunks total. Therefore, we need 4 exponent bits to be able to represent values 0 through 63. Given 4 exponent bits, the largest non-infinity/NaN exponent value (pre-bias) is  $2^4 - 2$ , which, after applying the standard bias of -7, is 7, which allows us to represent values up to 63.

If we used 3 exponent bits, the largest exponent value after applying the standard bias of -3 is 3, which cannot represent the value 63.

. 1 . . .

a ..

c

Anonymous Quetzal 12mth #1044abff

-) m

im also confused

$\bigcirc$  ...

...

Anonymous Magpie 12mth #1044acbb

ant

r 1

I'm also confused on this still.

Nikhil Kandkur staff 12mth #1044aeda

The standard bias for bias representation is  $-(2^{n-1}-1)$ , where n is the number of bits we have.

♡ …

Anonymous Emu 12mth #1044aafc 🗸 Resolved

[SU 23 Q 7] For this question part 7.2 how can we start task 6 while task 0 is still executing at hour 5?By this logic task 4 could be started at Hour 6.

#### Q7 Times Are Not to Scale

CodaBot is in charge of final exam logistics for 61C! Consider the following tasks:

| Task Number | Task                    | Time (hours) | Prerequisites |

|-------------|-------------------------|--------------|---------------|

| 0           | Write Exam              | 5            | -             |

| 1           | Conduct Review Sessions | 3            | -             |

| 2           | Send Seating Chart      | 1            | -             |

| 3           | Print Exam              | 2            | 0,1           |

| 4           | Proctor Exam            | 3            | 3             |

| 5           | Scan Exam               | 1            | 4             |

| 6           | Write Solutions         | 2            | 0             |

Q7.1 (2 points) Suppose CodaBot can only perform one task at a time. How long would it take for CodaBot to complete all these tasks by themselves?

**Solution:** 17 hours. Each task must be done sequentially, and there are 17 hours' worth of tasks.

Q7.2 (2 points) Now, suppose CodaBot can perform two different tasks at the same time. What is the minimum time it takes for CodaBot to complete all these tasks by themselves?

| Solution: 11 hours. Example task lis |             |             |  |  |

|--------------------------------------|-------------|-------------|--|--|

| Hour                                 | Active Task | Active Task |  |  |

| 0                                    | Task 0      | Task 1      |  |  |

| 1                                    | Task 0      | Task 1      |  |  |

| 2                                    | Task 0      | Task 1      |  |  |

| 3                                    | Task 0      | Task 2      |  |  |

| 4                                    | Task 0      | Task 6      |  |  |

| 5                                    | Task 3      | Task 6      |  |  |

| 6                                    | Task 3      |             |  |  |

| 7                                    | Task 4      |             |  |  |

| 8                                    | Task 4      |             |  |  |

| 9                                    | Task 4      |             |  |  |

| 10                                   | Task 5      |             |  |  |

$\bigcirc$  ...

Jero Wang STAFF 12mth #1044afcb

Sorry, it should start at hour 5, not hour 4.  $\odot$  …

Anonymous Cobra 12mth #1044aaec ( ✓ Resolved

```

[SP-23-Final-Q4.2 - Q4.4]

```

Could someone explain these three parts to me? Specifically, I don't get how we know all accesses to a and b miss for 4.2, and how the only misses are the 3 compulsory misses for 4.3 and 4.4.  $\odot$  …

Anonymous Pig 12mth #1044adae

For this question, I'm also wondering if we don't write "register int sum", would accessing sum count as accessing the cache?

$\bigcirc$  ...

Jero Wang STAFF 12mth #1044afee

Yes, it would.

♡ …

Anonymous Pig 12mth #1044affb

Replying to Jero Wang

What about when we're writing a for loop (int i = 0; ...). Then every time we access, i wouldn't that count as a cache access as well?

$\bigcirc$  ...

Jero Wang STAFF 12mth #1044baac

Replying to Anonymous Pig

Yeah...it would. That was not intentional, we should have put register there.  $\heartsuit$   $\cdots$

Anonymous Pig 12mth #1044baad

🔸 Replying to Jero Wang

in other cache couting problems though accessing "i" never counts as accessing the cache...

♡ …

#### Jero Wang STAFF 12mth #1044affa

a and b miss because we alternate between their accesses (access b, then a, then b, etc), and they have the same index, so they evict each other.

With the updated cache designs in Q4.3 and 4.4, the only misses are compulsory because the other misses we had (from index conflicts) are now resolved, as each index can hold 2 (for Q4.3) or 4 (for Q4.4) cache lines.

♡ …

#### Anonymous Emu 12mth #1044aacf ( ✓ Resolved

[SU 23 Q 4.2] How do we calculate how many trytes of data we have?Also how do we know that there are 3 entries total?

Regardless of your answer to the above question, assume that CoryBot has a direct-mapped trache with TIO breakdown of 7:1:2, while SodaBot has a direct-mapped (binary) cache with a TIO breakdown of 7:1:2.

Q4.2 (2 points) For each block in their trache, CoryBot stores the tag and 1 additional trit of metadata (invalid/valid/dirty). What is the total number of trits used by the trache? Express your answer in terms of powers of 2 and 3.

1 -

**Solution:**  $3 \cdot (2^3 + 3^3)$ Each entry must contain 7 trits for the tag, 1 trit for metadata, and  $3^2$  trytes ( $3 \cdot 3^2 = 3^3$  trits) of data. There are  $3^1$  entries total, for a total of  $3 \cdot (2^3 + 3^3)$  trits.

. . . .

····

R

#### Byron Yang 12mth #1044aadc

According to the TIO breakdown, there is 1 trit for the index. Since 1 trit can hold 3 different values (0, 1, and 2), we have  $3^1 = 3$  rows in our cache.

For the data, if we're counting metadata as well, we can just convert the final  $3 \times (2^3 + 3^3)$  trits into trytes using the fact that 1 tryte = 3 trits. This comes out to 35 trytes.

Anonymous Emu 12mth #1044aade

that process doesn't hold for the following problem though...

Q4.3 (2 points) For each block in their cache, SodaBot stores the tag and 2 additional bits of metadata (valid bit, dirty bit). What is the total number of bits used by the cache? Express your answer in terms of powers of 2 and 3.

**Solution:**  $2 \cdot (3^3 + 2^5)$ Each entry must contain 7 bits for the tag, 2 bits for the metadata, and  $2^2$  bytes  $(2^2 \cdot 2^3 = 2^5)$ bits) for the data. There are  $2^1$  entries total, for a total of  $2 \cdot (3^3 + 2^5)$  bits.

$\bigcirc$  ...

Byron Yang 12mth #1044aadf

🔨 Replying to Anonymous Emu

Hmm, could you explain your thought process? Where do you think it's not working?  $\odot~\cdots$

Anonymous Emu 12mth #1044aaef

Replying to Byron Yang

For the total entries shouldn't it still be 3^1 because our index bits hasn't changed?  $\odot~\cdots$

Byron Yang 12mth #1044aafb

🔸 Replying to Anonymous Emu

We're using bits now since we're dealing with SodaBot. Bits only take on 2 values and we only have 1 bit for our index, which means we have 2 entries total.  $\bigcirc$  ...

Anonymous Monkey 12mth #1044abbf

Can you explain where  $2^3 + 3^3$  comes from? I get that we have 7 trit from tag, 1 bit from metadata trit, and 1 trit from index and 2 trit from offset? Here I'm getting 11 trits to get 33 trits? Where is the additional trits coming from?  $\bigcirc$  1 ...

Anonymous Emu 12mth #1044aacc ( ✓ Resolved )

[SU 23 Q 2 Part 2]Could someone please explain what this code is doing? I'm really confused about what is happening.

```

1 store_nibble_protected:

2

# prologue omitted

3

mv s0 a0

4

mv s1 a1

5

srli s7 s0 1

# srai also acceptable

6

slli s7 s7 1

# make space for next bit

7

andi a0 s0 0b1110

# parity of d1, d2, and d3

8

jal ra calculate_parity

# compute p2

# xor and or also acceptable

9

add s7 s7 a0

10

slli s7 s7 1

# make space for next bit

11

andi t0 s0 1

# extract d0

add s7 s7 t0

# xor and or also acceptable

12

# make space for next bit

13

slli s7 s7 1

14

andi a0 s0 0b1101

# parity of d0, d2, and d3

15

jal ra calculate_parity

# compute p1

add s7 s7 a0

# xor and or also acceptable

16

17

slli s7 s7 1

# make space for next bit

18

andi a0 s0 0b1011

# parity of d0, d1, and d3

19

jal ra calculate_parity

# compute p0

20

add s7 s7 a0

# xor and or also acceptable

21

sb s7 0(s1)

# s1 contains the memory address

# passed in as a1

22

# epilogue omitted

23

jr ra

```

♡1 …

Jero Wang STAFF 12mth #1044afbe #1044acff  $\bigcirc$  ...

Anonymous Llama 12mth #1044aabc ( 🗸 Resolved )

Su23-Final-Q5.4

Given a Virtual Address, how do you determine what is the VPN,PPN, and Page Offset bits?  $\odot \ \cdots$

# Byron Yang 12mth #1044aadd

If you're just given the virtual address, I don't think you can figure out any of those things. You also need to know the page size.

For the VPN, we can figure out how big our virtual memory is from the size of the virtual address. If the size is n bits, we have  $2^n$  bytes in our virtual memory. We can then take this number and divide it by the page size to determine how many pages our virtual memory is. Then, we can do log(number of pages) to figure out how many bits we need to represent each of our pages. This gives us our VPN in our virtual address and we can do the same thing but with physical memory to get PPN.

To get the page offset, if we know the page size, we know how many bytes are in a page. We can then take the log of this number to get the number of bits needed to address each

individual byte. This is how many bits our page offset needs.

Hope this helps somewhat!

♡1 …

Anonymous Mule 12mth #1044aafe

I'm not the person who asked this but thanks so much!

...

Byron Yang 12mth #1044abab

Replying to Anonymous Mule

Glad to help :)

♡1 …

Anonymous Llama 12mth #1044abae

For this specific, where 0xA01243 is given as the Virtual Address I'm still a bit confused. We are told to assume that we have 20-bit physical memory addresses and 24-bit virtual memory addresses but not sure how that tells us that the VPN is 0xA01 and the offset is 0x243. If they tell us to disregard the answers above this question not sure how we can know there are 12 bits of offset..

♡3 …

Anonymous Monkey 12mth #1044abcc

Replying to Anonymous Llama AA

♡1 …

Anonymous Quail 12mth #1044acca

Replying to Anonymous Llama

I'm confused about the same thing!

1 ····

Anonymous Tapir 12mth #1044aefc 🛛 🤶 ENDORSED

Replying to Anonymous Llama

I think it tells us to disregard our answers, but we still need to use the fact that the pages are 4 KiB for question 5

...

Jero Wang STAFF 12mth #1044afcc

🔨 Replying to Anonymous Llama

#1044aefc We ask you to ignore your answers to Q8.1-8.4, not the initial problem setup.

$\bigcirc$  ...

Anonymous Echidna 12mth #1044aaba

Resolved

SU23-Final-Q8

Q8.5 (1.5 points) 0xC61

Solution: N/A

Since bits 11 and 0 are set, it cannot fit into a floating point number with 8 mantissa bits, so it is not representable.

Q8.6 (1.5 points) 0x200

#### Solution: 0x0A00

Each chunk is 64 bits, so that accounts for the lower 6 bits of the address, 0x00. The chunk address is the upper 6 bits of the address, is 0x08. We then must translate 0x08.00 to the floating point system described.

$0x08.00 = 0b1 \cdot 2^3$ , so the exponent is 0b1010 after applying the bias, and the mantissa is all 0's. This gives us 0x0A00.

I don't really understand the explanation for 8.5 and I also don't really understand why we know that the lower 6 bits of the address is the chunk and the chunk address is the upper 6 bits. Any help would be appreciated--thank you!

♡2 …

Anonymous Magpie 12mth #1044adce

Ditto

Jero Wang STAFF 12mth #1044afbc

We know that the lower 6 bits are the offsets within the chunk because each chunk is 64 bytes, and we need 6 bits to address each of the 64 bytes.

For 8.5, we know that given a FP system with 8 mantissa bits, the MSB and LSB must be at most 9 bits apart (i.e. 1.0000 0000 1). Since they are 12 bits apart, we don't have enough precision in this FP system to represent it.  $\bigcirc$  ...

#### SU23-Final-Q3.11

Jiries Kaileh 12mth #1044aaaf

AJ decides to deal with this problem by implementing new hardware and a new set of instructions, *long jump* and *long branch*. These instructions will allow offsets of up to 32 bits by storing the immediate in the 4 bytes immediately after the instruction within the IMEM, rather than within the instruction itself. To accommodate this, the IMEM has been modified to add another output port that contains the four bytes stored at addr + 4, where addr is the input to the IMEM.

✓ Resolved

Q3.11 (2 points) What additional changes would we need to make to our datapath in order for us to implement both of these instructions (with as few changes as possible)? Select all that apply.Assume that each of the options also include any relevant combinational logic and control logic additions or modifications.

For this question, I only filled in "add new input to the immediate generator". My idea was that if the branch failed, we could have RegWEn off for the Regfile and also have WBSel just set to PC+4 for the next instruction containing the 32-bit offset so you don't take the branch. Is this a feasible solution? the question does state "assume that each of the options also include any relevant combinational logic and control additions or modifications" and I believe that my method could be implemented in the control logic (albeit less efficient).

Jero Wang STAFF 12mth #1044afce

There's no way of detecting that the 32-bit offset is that offset without introducing additional logic and state elements, since the 32-bit offset could be an entirely valid RISC-V instruction as well.

$\odot$  ...

Anonymous Echidna 12mth #1044ffd ( < Resolved

SU23-Final-Q4

Q4.3 (2 points) For each block in their cache, SodaBot stores the tag and 2 additional bits of metadata (valid bit, dirty bit). What is the total number of bits used by the cache? Express your answer in terms of powers of 2 and 3.

Solution:  $2 \cdot (3^3 + 2^5)$ Each entry must contain 7 bits for the tag, 2 bits for the metadata, and  $2^2$  bytes  $(2^2 \cdot 2^3 = 2^5)$ bits) for the data. There are  $2^1$  entries total, for a total of  $2 \cdot (3^3 + 2^5)$  bits.

for this, why is it 3^3 in the parenthesis instead of 3^2? I thought since theres 7 bits for the tag and 2 bits for the metadata, that makes 9 (therefore 3^2) extra bits for each entry?  $\odot$  ...

```

N Nikhil Kandkur sTAFF 12mth #1044ffe

#1044cc

♡1 ···

Anonymous Mongoose 12mth #1044fed ✓ Resolved

```

```

SP23-Final-Q2.1

```

i'm confused about how we get the critical path, 855ps = τclk-to-q (35) + Immediate Generator (150) + Mux (75) + ALU (200) + Memory Read (300) + Mux (75) + τsetup (20)

isn't the immediate generator in the ID stage in the pipelined CPU on the reference card?  $\odot$  1  $\ \cdots$

N Nikhil Kandkur STAFF 12mth #1044ffc #1044bb  $\heartsuit$  ...

```

SU23-Final-Q2 Part 2

```

I read through the answer key for this and I kind of get the logic but not completely--do you think it would be possible to write out how a0 and s7 change on example input and explain it a bit more? Thank you so much!

♡1 …

Andrew Liu STAFF 12mth #1044babf So s7 starts out with all of a0 loaded into it:

s7 : 0 0 0 0 d3 d2 d1 d0

Then, we shift right then left to clear do:

s7: 0 0 0 0 0 0 d3 d2 d1 s7: 0 0 0 0 d3 d2 d1 0

Then, we calculate  $p_2$  and store it in the LSB, then shift left by 1 to open up space for the next bit:

s7: 0 0 0 0 d3 d2 d1 p2 s7: 0 0 0 d3 d2 d1 p2 0

Then, we repeat this pattern, grabbing the next desired bit and then shifting:

s7: 0 0 0 d3 d2 d1 p2 d0

s7: 0 0 d3 d2 d1 p2 d0 0

s7: 0 0 d3 d2 d1 p2 d0 p1

s7: 0 d3 d2 d1 p2 d0 p1 0

s7: 0 d3 d2 d1 p2 d0 p1 0

And at the end of this, we store it to the memory in a1. a0 keeps track of the relevant bits as we go, as needed:

```

a0: 0 0 0 0 (d3/0) (d2/0) (d1/0) (d0/0)

```

Anonymous Lion 12mth #1044fdc ( 🗸 Resolved )

#### SU23-Final-Q3.9

Is the implicit 0 considered part of the 12 bits, or does the immediate have 13 total bits? The formula for two's complement range is  $[-2^n-1, 2^n-1 - 1]$ , so I'm struggling to see where the  $2^n-1 - 2$  came from. Also, the formula only works if n = 13, but according to risc-v architecture branch immediates only have 12 bits. just generally confused about these range questions so any guidance would help!

♡ …

Byron Yang 12mth #1044feb

The implicit 0 is not considered in the 12 bits, so there are 13 bits total for branch immediates. To get the maximum positive jump, we need a 0 for our 12th bit (to make sure our number is non-negative) and 1's from the 11th bit to the 1st bit, then the implicit 0 for our 0th bit. The value of this is  $2^1 + 2^2 + ... + 2^{11}$ . To evaluate this, we can pretend that we have an implicit 1 rather than an implicit 0 in our 0th bit. This would make the value  $2^0 + 2^1 + 2^2 + ... + 2^{11}$ . Using some math

(https://math.stackexchange.com/questions/1990137/the-idea-behind-the-sum-of-powers-of-2), this is equal to  $2^{12} - 1$ . Now since we don't actually have an implicit 1, we subtract this quantity by 1 to get the desired  $2^{12} - 2$  as our largest positive jump.  $\bigcirc$   $\cdots$

#### Anonymous Dove 12mth #1044abcf

what is a good way to think about this question? I was completely lost when I looked at it first. Where did two's complement come from and and is this 2 to the power of the branch immediates

♡ …

I get that the largest positive jump is  $2^{12} - 2$  but how is the answer then  $2^{12}$  in the solutions

♡ …

Anonymous Tapir 12mth #1044afba

🔷 👆 Replying to Anonymous Lobster

The negative jump is 2^12 and we want the largest, which is why the solution is 2^12  $\odot_1 \ \cdots$

SP23-Final-Q4.5

Don't we need to multiply hit rates by access times? Previously, AMAT = (L1 hit rate)(L1 access time) + (miss rate)(main memory access time).

Shouldn't the first computation be (0.75 \* 6)? The solution only uses miss rates.  $\odot$  ...

# Nikhil Kandkur staff 12mth #1044ffb

Our formula for AMAT should be L1 access time + (miss rate \* main memory access time), since we are always going to look into the L1 cache, and only if we miss look into memory.  $\odot$  …

Anonymous Swallow 12mth #1044faf ( < Resolved

SU23-Final-Q6

I'm having some trouble understanding why we are using width = right - 4 and why we keep incrementing and decrementing left and right by 4. Is it because we are comparing each of the arrays 4 elements at a time, working our way from the endpoints to the middle?  $\odot$  ...

Jiries Kaileh 12mth #1044aacd

To add on to this, why are we not assigning right = (width - 4) \*sizeof(uint32\_t) and incrementing the points by 4 \* sizeof(uint32\_t)? Is this because left and right are automatically multiplied by this when doing pointer arithmetic?

Thanks!

○ …

Jero Wang STAFF 12mth #1044addd Yep

○ …

Anonymous Lion 12mth #1044aaff same question

○ …

Anonymous Chimpanzee 12mth #1044abba

instead of vecReverse(vecLoad(matrix[i]+right)) in line 10, would it work if we just loaded the vector here and then reversed in the arguments for vecEq in line 11?

--> line 11: vecEq(vec1, vecReverse(vec2))

Also: What is the difference between vecLoad(matrix[i]+left) and vecLoad(\* (matrix[i]+left)) and vecLoad(\*(matrix+i+left))? ♡ … Jero Wang STAFF 12mth #1044adea Replying to Anonymous Chimpanzee Yes, that works. matrix[i] + left indexes into matrix then adds an offset of left elements, while the second option dereferences the result (so it would be the same as matrix[i] [left]). The last option doesn't index into matrix, instead returning matrix offset by i + left elements. ♡1 … Jero Wang STAFF 12mth #1044adde Yep exactly  $\bigcirc$  ... SP23-Final-Q7 I just have no idea how to answer it. Any hints about how to deal with questions like this? Where

should I start?

Thanks!

$\bigcirc$  ...

– N Nikhil Kandkur staff 12mth #1044fbb

From my side, my main tip for solving the problem is to read the question and code outline carefully: since we can "null terminate" our array with a 0, then we can consider an approach that involves in us continuing to use a copy of an array, and set our branch/jump instructions to 0. The code outline gives us this hint, and in addition tells us that we can keep using the same array, but in fact set our pointer values to various points in the array, rather than making several extra copies of memory.

If you have further questions, please look around the megathread, as there are several comments that provide insight into the problem. You may also reply to this thread if you have questions the other comments couldn't answer.

♡2 …

Anonymous Grasshopper 12mth #1044fbe help a lot! thanks

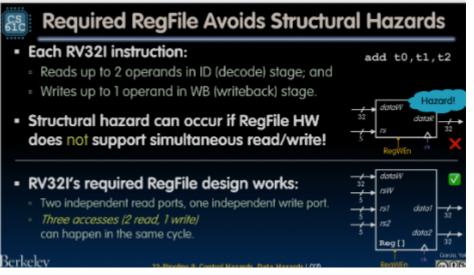

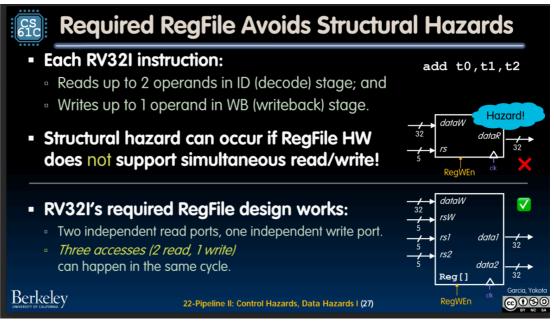

Anonymous Pheasant 12mth #1044eef ( ✓ Resolved SU23-Final-Q8.1: can you explain where the standard bias of -7 comes from? is there an equation we shoujld use to calculate standard bias? I am very confused on bias in general. What should we know about it? ···· Anonymous Cod 12mth #1044aaae The standard bias is calculated as -(2^(n-1)-1) where n represents how many bits the exponent has. I noted that from one of the course staff's slides. It's also shown on the third page of the ref Card.  $\bigcirc$  ... Anonymous Dinosaur 12mth #1044eed ( 🗸 Resolved SU23-Final-Q8.6 the solutions say "0x08.00 = 0b1.2^3, so the exponent is 0b1010 after applying the bias" how do we go from 4 exponent bits, with a bias of -7(?) to 0b1010? and where does the 8 come into this? thank you! ♡1 … Anonymous Rhinoceros 12mth #1044acbf ^ bump I have the same question  $\bigcirc$  ... Jero Wang STAFF 12mth #1044addb  $0 \times 08.00 = 0b \ 0000 \ 1000.0000 \ 0000$ , which can be simplified to  $0b1000 = 1.0 \times 2^{3}$ . After we apply a bias of -7 to the exponent of 3, we get 10, which is 0b1010.  $\bigcirc$  ... Anonymous Ferret 12mth #1044ecb 🗸 🗸 Resolved SP23-Final-Q2.4 After going over relevant threads, I'm still confused as to why structural hazards can't occur. If we add another RegFile, can't we read from one and write to another? When the problem says that we can't read from and write to Regfile in the same clock cycle, does it mean reading from and writing to the same Regfile, or any two Regfiles?  $\bigcirc$  ... Anonymous Magpie 12mth #1044ecc I have the same question as well.  $\bigcirc$  ... Nikhil Kandkur staff 12mth #1044efd N Even if we read from one and write to another, we would have to keep trying to make the regfiles the same values, which is time and energy consuming. Someone else in the threads cited this from discussion which helps with this: Through adding additional hardware, we can implement two 'read' ports as well as a 'write' port to the RegFile (where registers can be accessed). This solves the hazard of two instructions reading and writing to the same register

simultaneously. False. The addition of independent ports to the RegFile allows for multiple instructions to access the RegFile at the same time (such as one instruction reading values of two operands, while another instruction is writing to a return register). However, this does not work if both instructions are reading and writing to the same register. Some solutions to this data hazard could be to stall the latter instruction by 1 cycle or to forward the read value from a previous instruction, bypassing the RegFile completely

♡ …

# Anonymous Ferret 12mth #1044eff

The discussion solutions only mentioned that instructions which write to then read from the same register can't be solved by adding a Regfile. However, if we're reading from and writing to different registers, adding a Regfile can help address this issue. Therefore reading from and writing to different registers would still be considered a structural hazard, but it seems like that's not the case. Even if it were time and energy consuming, it could still be solved by adding a Regfile.

$\bigcirc$  ...

# Nikhil Kandkur STAFF 12mth #1044fba

🔨 Replying to Anonymous Ferret

The hazard of not being able to write and read in the same cycle is not one that is structural: we are not in the case where there are less ports than available for reading and writing to instructions. For our regfile, we will still have the 2 read ports and 1 write port, which will allow us to write and read to/from the same resource, so we will not have a case where we need more ports than there already are. We therefore have to treat this hazard as a data hazard since this is not structural.

$\bigcirc$  ...

# Hayden Loarie 12mth #1044fca

#### 🔦 Replying to Nikhil Kandkur

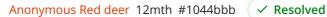

- 1. Structural Hazards

- a. More than one instruction needs to use the same datapath resource at the same time

- i. Register File

- ii. Memory (Instructions and Data)

- b. Solution: Double Pumping, Have more resources

This is from todays review session. Wouldn't this issue be solved with Double Pumping so we could write to the register file and then read right after?  $\odot$  ...

# Nikhil Kandkur STAFF 12mth #1044fda

Replying to Hayden Loarie

Theoretically, but they did say that that could not happen (writing and reading in the same cycle is not allowed for this problem).

$\bigcirc$  ...

# Hayden Loarie 12mth #1044fdd

Replying to Nikhil Kandkur

I guess I'm still confused about the problem then. From this slide Double Pumping is a solution to Structural Hazards. The issue that arose in the problem is because we don't have Double Pumping, so shouldn't it be a structural hazard?

Or should Double Pumping have been listed as a solution to Data Hazards instead?

Or am I just misunderstanding both things?  $\odot \ \cdots$

- A Aryansh Shrivastava 12mth #1044abcd

- Replying to Hayden Loarie

I'm confused as well. If we could theoretically solve the problem of not being able to read and write from the Regfile in the same clock cycle by changing the hardware to make the Regfile allow read and write in the same clock cycle (double pumping as above), doesn't that make this a structural hazard? (I'm not proposing we add a second Regfile or anything, but that we replace the original.)

Even our lecture slides specifically classify not supporting simultaneous read/write as a hardware issue that creates a structural hazard:

♡1 …

- Aryansh Shrivastava 12mth #1044abfd

- Replying to Aryansh Shrivastava

It would be really helpful if we could get a clarification on this before the final because this could potentially impact how we interpret problems on the final!  $\odot$  ...

- Julia Tomaszewska 12mth #1044accb

- 🔦 Replying to Aryansh Shrivastava

I would also appreciate an explanation about this, since I'm also confused.  $\bigcirc$  1  $\ \cdots$

- Nikhil Kandkur STAFF 12mth #1044adcd

- 🔨 Replying to Hayden Loarie

After talking to the other TAs for help on this, and they've confirmed that double pumping is a solution for data hazards, not structural hazards.  $\odot$  ...

Anonymous Ferret 12mth #1044aebb

🔨 Replying to Nikhil Kandkur

Is this the correct interpretation:

If our regfile does not have enough ports for simultaneous read/write (e.g. it only has a read port or only has a write port), then this constitutes a structural hazard since it can

be resolved by adding more ports or changing the structure of our regfile.

However, if our regfile already has both read ports and write ports, then we consider the following two situations: 1) one instruction writes to a register and the following instruction reads from a different register. This behavior is supported by our current regfile and not the aforementioned regfile, therefore if we were using the regfile that did not support simultaneous R/W, this would be a structural hazard. 2) one instruction writes to a register and the following instruction reads from the same register. Our new regfile does not support this kind of behavior, and this cannot be resolved by adding regfiles, either. Therefore this constitutes a data hazard, and can be resolved by double pumping, i.e. write-then-read in a clock cycle.

The main takeaway should be: if we can resolve the hazard by adding more hardware (i.e. adding more regfiles or adding more ports to the regfile), then the hazard is a structural hazard.

$\bigcirc$  ...

Jero Wang STAFF 12mth #1044afcf Replying to Anonymous Ferret Yes, that's correct.

$\bigcirc$  ...

Anonymous Lark 12mth #1044afcd

🔨 Replying to Nikhil Kandkur

Are we supposed to ignore the lecture slides + final exam review session slide then?  $\odot~\cdots$

Jero Wang STAFF 12mth #1044afda

Replying to Anonymous Lark

Which lecture slide? I'll ask the final review team to update the review slides.  $\odot~\cdots$

Anonymous Lark 12mth #1044afdc

Replying to Jero Wang

Wouldn't this slide imply that structural hazard should be selected in the exam question? "Structural hazard can occur if RegFile HW does not support simultaneous

read/write"

♡1 …

Anonymous Crane 12mth #1044acfa

Replying to Nikhil Kandkur

Same question here!

3 ···

Anonymous Magpie 12mth #1044eca ( 🗸 Resolved

Sp23-Final-Q7:

$\bigcirc$  ...

Why is the \*codecopy = 0 necessary in this code solution.

From my understanding, we are looping through codecopy and whenever we see a jump/branch instruction, we set a data pointer to the next instruction to mark a new segment. Then, we continue to iterate through codecopy and do the same thing as needed -> until we hit the null terminator.

If that's the case, what good does setting \*codecopy = 0 here do.?  $\odot \ \cdots$

Nikhil Kandkur STAFF 12mth #1044eea

We would have to do \*codecopy = 0 since that sets a "null terminator" for our portion of the list. If we have a list [add x0 x0 x0, slli x2 x2 1, beq x1 x2 label1, add x0 x1 x2], after our code we would have [add x0 x0 x0, slli x2 x2 1, NULL, add x0 x1 x2], and this is valid since we specify that

Each of these arrays should be "null-terminated"; that is, the last element of each array should be the number 0, to signify the end of the array.

Anonymous Cassowary 12mth #1044aabb can we do codecopy[0] = 0 instead?

Nikhil Kandkur STAFF 12mth #1044aabe

Anonymous Cassowary 12mth #1044aacb

🔸 🔨 Replying to Nikhil Kandkur

Thanks! also for the very last blank of that question i did result = &data instead of \*result = data, would that be fine?

$\bigcirc$  ...

Nikhil Kandkur STAFF 12mth #1044aace

Replying to Anonymous Cassowary

That would NOT work, because result = &data only sets the local copy of result to &data . When we return from the function, the value we created will not be there as a result. \*result = data sets the value stored at the pointer to data, which will carry on after returning the function.

♡1 …

### SP-23-Final-Q2.1, 2.1

Why for the critical path occurs in stage 2 for a load instruction we don't need to add Regfile Setup?

855ps = τclk-to-q (35) + Immediate Generator (150) + Mux (75) + ALU (200) + Memory Read (300) + Mux (75) + τsetup (20)  $\bigcirc$  ···

\_ Anonymous Oryx 12mth #1044ece

by the way, is there a case that we need to add both tsetup (20) and Regfile Setup (20) when we calculate the minimum operating clock period.

$\bigcirc$  ...

Nikhil Kandkur staff 12mth #1044efe

$au_{setup}$  = time for Regfile setup so it wouldn't matter which setup time we add.

For your second question, there is not a case when we would have to add both  $\tau_{setup}$ and Regfile setup since even in the single cycle datapath, you can have the PC setup either happen at the same time of Regfile setup or before Regfile setup (and at the same time as some other combinational logics).

♡ …

Anonymous Horse 12mth #1044abaf

🔷 🔸 Replying to Nikhil Kandkur

Why do we factor in the immediate generator into this calculation? I thought that it would be in the ID stage (stage 1 of the problem).

$\bigcirc$  ...

N Nikhil Kandkur STAFF 12mth #1044abbe

Replying to Anonymous Horse

#1044bb

$\bigcirc$  ...

Anonymous Chicken 12mth #1044ebb 🗸 🗸 Resolved

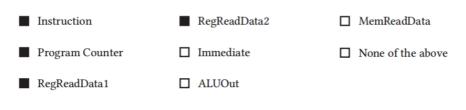

Q2.3 (3.5 points) In the CPU, which of the following values must have a pipeline register? Select all that apply.

**Solution:** The values that require a pipeline register are all values generated in stage 1, which are Instruction (from IMEM), Program Counter (from the PC register), RegReadData1 (from Regfile) and RegReadData2 (also from Regfile). The remaining three values are all outputs of components in the second stage of our pipeline.

**Grading:** Each checkbox was graded as it's own true/false question, and selecting "None of the above" was treated as not selecting any of the other choices.

Sp23-final-Q2, why the values that require a pipeline register are all values generated in stage 1, rather than Instruction, Program Counter, RegReadData1, RegReadData2, Immediate, ALUOut, and MemReadData?

0 ...

# - N Nikhil Kandkur STAFF 12mth #1044fac

Remember that we have to construct our pipeline such that stage 1 and stage 2 are separated, which means that any values we send from stage to another need to be sent into a pipeline register and the values from the pipeline registers will be used in the next stage. When going from stage 1 to stage 2, the only values that are generated in stage 1 that are used in stage 2 are Instruction (for control logic), Program Counter (for PC input into A Mux and PC + 4), RegReadData1 (for A Mux), and RegReadData2 (for B Mux and memory). Hope this helps!

$\bigcirc$  ...

Anonymous Sand Dollar 12mth #1044ead ( 🗸 Resolved )

#### Sp23-Final-Q7:

After we set \*codecopy to 0 for 7.12, how does this allow our data[i]'s to be set correctly? I get that the code saves the initial codecopy address and then we scan through all the valid instructions. Then, when we hit the first invalid element (it's either equal to 0 or it's a jump or branch instruction), we stop and zero it out. However, after doing this, wouldn't our data[i] include all the remaining elements in our array, even those that extend beyond the 0 we set? What's ensuring our data[i]'s stop at those 0's?

♡1 …

# Nikhil Kandkur STAFF 12mth #1044edd

Yes data[i] would contain the remaining elements in our array, but if you were to print the values of these lists, since we are setting a "null terminator" in our list, and we specified that

Each of these arrays should be "null-terminated"; that is, the last element of each array should be the number 0, to signify the end of the array.

Anonymous Sand Dollar 12mth #1044faa

I thought stopping when hitting the null terminator was something that only applied to char\* arrays. Do int\* arrays also follow this behavior?

$\bigcirc$  ...

···· ()

Nikhil Kandkur STAFF 12mth #1044fad

Replying to Anonymous Sand Dollar

No, we can only do what we did because we specified that you can set 0 to be a null terminator.

♡1 …

$\bigcirc$  ...

Anonymous Sand Dollar 12mth #1044fae

🥌 🕤 Replying to Nikhil Kandkur

Oh ok thank you Nikhil!

Anonymous Salmon 12mth #1044eaa ( ✓ Resolved

# SU23-Final-Q8.1

I read the explanation: The answer says that those bits would be the exponent bits, so given standard bias, we would need 4 exponent bits to represent 63 in our IEEE-754 FP standard.

but I am not sure how that works still.  $2^4+2^3+2^2+2^{1}+2^0$  will still not attain 63 but only 31?  $\odot$  4 ...

#### Jero Wang STAFF 12mth #1044adcc

The question is asking about how many exponent bits it takes to represent numbers up to 63 in a FP system. To reach 63, the exponent must be at least 5, post-bias ( $2^5 \times 1.11111 = 63$ ). As a result, to get a post-bias exponent value of 5, we need at least 4 exponent bits.  $\bigcirc$  ...

#### Anonymous Clam 12mth #1044adec

Why can't we use 3 bits to get a post bias exponent value of 5? Also what would the pre-bias exponent value be and how would we find that? Sorry I am just a bit confused because I thought that we usually shift the binary representation and then add the bias but here you seem to be saying that 5 must be exponent after we add the bias and also seem to be shifting the binary representation by 5? A clarification would be helpful.  $\bigcirc$  …

#### Anonymous Ferret 12mth #1044dff ( ✓ Resolved

#### SU23-Final 7

Is question 7 just trial and error or is there a general approach to dividing the work. I know that we want to minimize the time any worker is "idle". Is this optimized by having all pre-reqs done first, etc or is there no stand-by algorithm

♡ …

#### Jero Wang STAFF 12mth #1044adcb

Yeah, somewhat trial-and-error, but you should use heuristics like the one you mentioned where you minimize the amount of time that each worker is idle. Generally, a greedy algorithm is enough for these questions, or at least they will give you a good starting point to make small modifications.

♡ …

Anonymous Ferret 12mth #1044dfe ( ✓ Resolved

SP23-Final-Q2

Why is the Immediate Generator part of EX and not ID? Why is it included in the longest path calculation for load operations in stage 2?

Anonymous Starling 12mth #1044ebc #1044bb  $\bigcirc$  ... Anonymous Ferret 12mth #1044dfb ( ✓ Resolved SP23-Final-Q7.7 Solutions should say i < num + 1 instead of num + 1.  $\bigcirc$  ... Nikhil Kandkur STAFF 12mth #1044edb N Yup! Sorry about that  $\bigcirc$  ... Anonymous Rail 12mth #1044def ( ✓ Resolved SP23-Final-Q7: for(int i = 0; \_\_\_\_\_\_ 15 ; i++) { 07.7 16 data[i] = \_\_\_\_\_ 07.8 while(\_\_\_\_\_\_\_Q7.9 17 \_\_\_\_&&\_\_\_\_ 07.10 18 Q7.11 19 } 20 Q7.12 21 codecopy++; 22 }

What exactly is this second for loop doing?

23

$\bigcirc$  ...

$\bigcirc$  ...

Anonymous Sand Dollar 12mth #1044eab

From my understanding, it checks whether the current instruction at address codecopy is "valid" (it isn't a jump or branch instruction and it's not a 0) and if so, increments codecopy. So we skip through all the valid instructions starting at address codecopy essentially.  $\bigcirc$  ...

\_\_\_\_ != 0) {

;

Anonymous Salmon 12mth #1044dee ( 🗸 Resolved )

#### SU23-Final-Q4.2,Q4.3

Why do we assume the offset bits are in tryte or bytes while the tag and index are in trit and bits? Because we could directly write in the number of index+offset but then for the offset had to convert to trit or bit

♡1 …

Jero Wang STAFF 12mth #1044adca

Each cache line needs to store the tag itself (so it knows what the tag of the data is), whereas the data is storing the actual data, which is in terms of bytes/trytes. While the size of data is related to offset, you're not directly storing the offset.

$\bigcirc$  ...

Anonymous Caterpillar 12mth #1044dec ( ✓ Resolved

# SP23-Final-Q7.9-7.12

For 7.9, how does referencing codecopy give a single instruction that we can then input into isBranchJump? For 7.10, why are we checking is the dereferenced codecopy is not equal to 0? Also what does codecopy++ do in 7.11? Also what is line 7.12 doing?

#### Solution:

```

Q7.1: instruction & 64

Q7.2: i < n

Q7.3: isBranchJump(code[i])

Q7.4: sizeof(int*) * (num + 1)

Q7.5: sizeof(int)

Q7.6: sizeof(int) * n

Q7.7: num + 1

Q7.8: codecopy

Q7.9: !isBranchJump(*codecopy)

Q7.10: *codecopy

Q7.11: codecopy++

Q7.12: *codecopy = 0

Q7.13: *result = data

Q7.14: num + 1

```

#### ♡1 …

#### Anonymous Ferret 12mth #1044eac 🛛 😣 ENDORSED

From a high-level perspective, we want to scan over all lines of code and determine what gets put into the array we return. The purpose of having codecopy is that we are able to use it to keep track of which line we've scanned up to (notice that codecopy gets incremented in the for loop).

Q7.9: codecopy initially points toward the first line of code, since we performed a memcpy operation. After that, notice how in each iteration of the for loop, data[i] and the initial value of codecopy points towards the instruction right after a jump/branch instruction. In the subsequent parts of each for loop iteration we are essentially trying to find where the following jump/branch instruction is, and have codecopy point to the instruction after that, so that the next data[i] again points to the instruction right after a jump/branch.

Q7.10: calloc allocates n+1 values. After memcpy, the last element of the codecopy array is a 0. If we didn't check for \*codecopy != 0 when codecopy points to this last element, since isBranchJump(0) is 0, we would increment codecopy and end up outside of the codecopy array.

Q7.12: A good way to go about looking at this is that you could compare the RISC-V code in the problem statement with the sample array right below it. If you match each element of the array with the RISC-V code, (i.e. in this example, 0 with beq x0 x0 pass, 0 with beq x0 x0 pass, add a0 t0 t1 with add a0 t0 t1, so on and so forth), you can notice that the array we

return contains all instructions but with the jump/branch instructions zero-ed out. This is an interesting side effect of null-terminating the array as mentioned in the problem statement. \*codecopy=0 makes this possible.

♡1 …

Nikhil Kandkur STAFF 12mth #1044eeb

Great explanation! I also wanted to add that for 7.12, we specified in the question description that

Each of these arrays should be "null-terminated"; that is, the last element of each array should be the number 0, to signify the end of the array.

So just setting our value to 0 in our array would still be valid as a "null terminator".  $\bigcirc$  1  $\ \cdots$

```

Anonymous Sand Dollar 12mth #1044deb

```

```

Sp23-Final-Q7.1:

```

Would checking if (instruction AND 127 == 99) or (instruction AND 127 == 103) or (instruction AND 127) == 111 work for this question? Also, for the solution, do we AND by 64 because all instructions besides jumps and branches (and ignoring ebreaks and ecalls) have the first digit of their opcode as 0? Thanks!

♡1 …

Justin Yokota STAFF 12mth #1044eba

The first two parts do not work as intended because == has higher operator precedence than AND, and you would get marked off for incorrect AND/OR syntax. Otherwise, this should be fine if it matches the reference card.

$\bigcirc$  ...

SP23-6.3:

Q6.3 (1 point) We want to send **one** bit using a Hamming error correcting code. What are the valid bit patterns you could send that correspond to 0b0 and 0b1?0b0: 0b1:

**Solution:** Each Hamming error correcting code must be at least 3 bits (two parity bits, one data bit). The ECC for 0b0 is 0b000 and for 0b1 is 0b111. **Grading:** All or nothing for each answer box.

Wouldn't 0b1 as 0b111 be incorrect bc there are an odd number of bits when checking the hamming code?

Shouldn't there be multiple valid solutions?  $\odot \ \cdots$

\_ •

Anonymous Starling 12mth #1044ebe

If I'm understanding your question correctly, 0b111 is the only correct answer for a data bit of 0b1 since we need to have 3 bits for any Hamming error correcting code (data only starts

on the third bit). Therefore, if we set 0bxx1, then both the first and second bits are 1 as follows by parity. Hope this helps!  $\bigcirc$  ... Anonymous Rail 12mth #1044ecd This makes sense. Thanks!  $\bigcirc$  ... Anonymous Rail 12mth #1044ddd ( ✓ Resolved SP23-Final-Q4: we have a[i + j], b[j], and results[i] as accesses. Do we store (i, j, i+j), (a[i + j], b[j], results[i]) or (0x1000, 0x2000, 0x3030) in cache? How do we know 'what type of data' we store in cache?  $\bigcirc$  ... Nikhil Kandkur STAFF 12mth #1044fbc N We would have to store the memory at the addresses we are loading/storing from in our cache, so that would be (a[i + j], b[j], results[i]). ···· ·· Anonymous Caterpillar 12mth #1044ddc ( ✓ Resolved Q6.3 (1 point) We want to send **one** bit using a Hamming error correcting code. What are the valid bit patterns you could send that correspond to 0b0 and 0b1? 0b0: 0b1:

**Solution:** Each Hamming error correcting code must be at least 3 bits (two parity bits, one data bit). The ECC for 0b0 is 0b000 and for 0b1 is 0b111. **Grading:** All or nothing for each answer box.

### SP23-Final-Q6.3

How do we know that the Hamming error correcting code must be at least 3 bits? I'm not sure how to determine that

♡3 …

Anonymous Rail 12mth #1044ddf **Rendorsed**

| Bit posit                 | ion     | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14  | 15  | 16  | 17  | 18  | 19  | 20  |  |

|---------------------------|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|--|

| Encoded da                | ta bits | p1 | p2 | d1 | p4 | d2 | d3 | d4 | p8 | d5 | d6 | d7 | d8 | d9 | d10 | d11 | p16 | d12 | d13 | d14 | d15 |  |

| Parity<br>bit<br>coverage | p1      | 1  |    | 1  |    | 1  |    | 1  |    | 1  |    | 1  |    | 1  |     | 1   |     | 1   |     | 1   |     |  |

|                           | p2      |    | 1  | 1  |    |    | 1  | 1  |    |    | 1  | 1  |    |    | 1   | 1   |     |     | 1   | 1   |     |  |

|                           | p4      |    |    |    | 1  | 1  | 1  | 1  |    |    |    |    | 1  | 1  | 1   | 1   |     |     |     |     | 1   |  |

|                           | p8      |    |    |    |    |    |    |    | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   |     |     |     |     |     |  |

|                           | p16     |    |    |    |    |    |    |    |    |    |    |    |    |    |     |     | 1   | 1   | 1   | 1   | 1   |  |

The parity bits p1 and p2 correpond to d1, so the code should be composed of p1, p2, d1  $\odot$  2  $\cdots$

### SP23-Final-Q4.2

How do we know that "For each set of accesses to an and b, the program experiences thrashing since the index of these blocks conflict"? How do we use a=0x1000, b=0x2000, and

results=0x3030, to determine thrashing/index conflicts?  $\odot \ \cdots$

### – <sub>NI</sub> Nikhil Kandkur staff 12mth #1044fbf

There is no mathematically formal definition for thrashing: thrashing is when we consistently have misses when in our accesses due to the structure of our code. If we see how we access our code, we see consistent misses for a and b, which fits our definition of thrashing. a=0x1000, b=0x2000, and results=0x3030 tells us that our addresses are located far away from each other, so that means that if we have to access anything from those arrays, they will require separate cache blocks. In addition, we can make our TIO breakdown from this, and see that there is a lot of conflicts due to this.

$\bigcirc$  ...

### Anonymous Opossum 12mth #1044aadb

Why do they conflict if they are stored in separate cache blocks?  $\bigcirc$  6  $\cdots$

Anonymous Echidna 12mth #1044abbc

Replying to Anonymous Opossum

I am also confused about this! If they are located farther from each other then why would that cause thrashing? Wouldn't it be better if they were farther away because then there are less conflicts?

$\bigcirc$  ...

Anonymous Echidna 12mth #1044abbd

🔨 🔨 Replying to Anonymous Echidna

or is it because both of them have the same index (0) that the conflicts occur?  $\odot~\cdots$

Jero Wang STAFF 12mth #1044adbe

Replying to Anonymous Echidna

Not necessarily farther, but the addresses here are specifically chosen such that their indexes conflict. I think if b was at  $0 \times 2010$ , they won't thrash anymore.  $\bigcirc$  ...

## Jero Wang STAFF 12mth #1044adbd

Replying to Anonymous Opossum

They conflict because they have the same index.  $\bigcirc \ \cdots$

### Anonymous Kookabura 12mth #1044babc

🔸 Replying to Jero Wang

Still couldn't understand this - why is thrashing happening? I'm not sure why they have the same index (as for b we are indexing j and for a we are indexing i+j)  $\odot$  ...

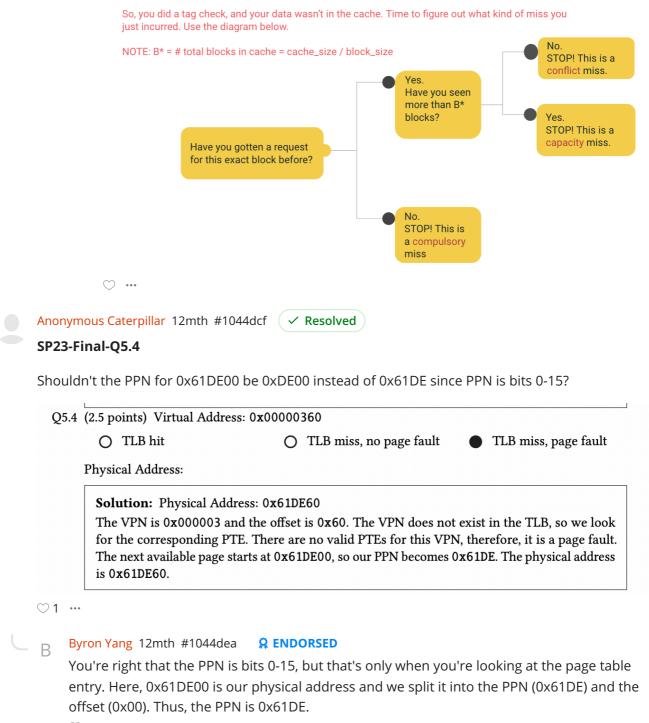

### Anonymous Squid 12mth #1044dda ( 🗸 Resolved )

for capacity miss, does the whole cache need to be filled? if the specific index is filled but there are open slots for other indices and we want to use the specific index for a different tag is it a capacity or conflict miss

♡ …

#### Anonymous Starling 12mth #1044ebf

Yes. In the case you described, it would be a conflict miss. You can think of capacity misses as misses which would be resolved if we increased the size of the cache.  $\odot$  ...

Nikhil Kandkur STAFF 12mth #1044eda

Yup! I included a infographic that helps identify the differences between misses on my discussion slides. Hope this helps!

# **Classifying Misses**

$\bigcirc$  ...

```

Is num_cols - 3 acceptable for Q3.2? And is vec_load(matrix + i + j) acceptable for Q3.4?

\bigcirc ...

Anonymous Grasshopper 12mth #1044dbe

vec_load(matrix + i*col_nums + j)

\bigcirc ...

Nikhil Kandkur STAFF 12mth #1044fcb

For your first question, I'm not too sure how num_cols - 3 will still give us a way to

handle the tail case.

For your second question: #1044efc

\bigcirc ...

Anonymous Grasshopper 12mth #1044aabd

🔦 🔨 Replying to Nikhil Kandkur

For tail case, we still start loop from num_cols / 4 * 4, is it ok?

\bigcirc ...

Nikhil Kandkur STAFF 12mth #1044aabf

Replying to Anonymous Grasshopper

Hmm that might be able to work, but it would be best and safer if you set your end

condition to num_cols/4*4

♡ …

Anonymous Grasshopper 12mth #1044aaca

🥌 🔦 Replying to Nikhil Kandkur

got it, thx!

\bigcirc ...

Anonymous Pig 12mth #1044aaea

If we did num_cols - num_cols % 4 instead of num_cols / 4 * 4 is that ok?

\bigcirc ...

Jero Wang STAFF 12mth #1044adbc

Yeah, that's fine too.

\bigcirc ...

Xiaole Guo 12mth #1044dae ( ✓ Resolved

Х

SP23-Final-Q9

following IEEE-754 convention, with 5 exponent bits, if the exponent bits and mantissa bits are all

0, then it represents the object 0 right? That's why if the 19-bit input is all zeros, we can still say

that it can be represented as a 19-bit float following IEEE-754 convention with 5 exponent bits?

```

$\bigcirc$  ...

Anonymous Chimpanzee 12mth #1044dce I don't understand this solution, can someone explain it? Jero Wang STAFF 12mth #1044adbb

This should work for the 0 answer, since all bits are 0, the expression in the NOT evaluates to 0, and after NOT returns a 1.

$\bigcirc$  ...

Xiaole Guo 12mth #1044dad 🗸 Resolved

#### SP23-Final-Q6.4

for the third statement which is selected, indeed the knowledge is covered in lecture 35. But in lecture 35, I don't think the ppt states that if checksum is not correct, then an error is either in the payload or the checksum. I just wonder where the lecture slides mentions what an incorrect checksum implies?

$\bigcirc$  ...